## MAINTENANCE HANDBOOK

4808

Multifunction Calibrator

### MAINTENANCE HANDBOOK

for

# THE DATRON 4808 MULTIFUNCTION CALIBRATOR

Att. Mary 19

# Part 1 - Calibration and Servicing Information

and

Part 2 - Technical Descriptions

For any assistance contact your nearest Datron Sales and Service center.

Addresses can be found at the back of this handbook.

850277

Issue 1 (MAR 1992)

Due to our policy of continuously updating our products, this handbook may contain minor differences in specification, components and circuit design to the instrument actually supplied. Amendment sheets precisely matched to your serial number are available on request.

© 1992 Datron Instruments

This product complies with the requirements of the following European Community Directives: 89/336/EEC (Electromagnetic Compatibility) and 73/23/EEC (Low Voltage) as amended by 93/68/EEC (CE Marking).

However, noisy or intense electromagnetic fields in the vicinity of the equipment can disturb the measurement circuit. Users should exercise caution and use appropriate connection and cabling configurations to avoid misleading results when making precision measurements in the presence of electromagnetic interference.

## DANGER HIGH VOLTAGE

# THIS INSTRUMENT IS CAPABLE OF DELIVERING A LETHAL ELECTRIC SHOCK!

I+, I- Hi and Lo terminals

Carry the Full Output Voltage

THIS CAN KILL!

Guard terminal is sensitive to over-voltage

It can damage your instrument!

Unless you are sure that it is safe to do so,

DO NOT TOUCH

the I+ I- Hi or Lo leads and terminals

DANGER

#### CONTENTS

| Servicing            | Diagrams and Component Lists Refer to Volume                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <del>)</del> 2                                                                                  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| General<br>Applicati | Description, Installation , Controls, Connections and Operation,<br>Ins, Specification, Specification Verification and Routine Calibration                                                                                                                                                                                                                                                                                                                                                                                                   | Handbook                                                                                        |

| PART                 | 1 CALIBRATION AND SERVICING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                 |

| Section              | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                                                            |

| 1                    | CALIBRATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                 |

|                      | .1 Guide to Calibration2 Remote Calibration Guidelines3 Pre-Calibration:                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 1-7<br>. 1-9<br>. 1-10<br>. 1-13<br>. 1-14                                                    |

| Ż                    | FAULT DIAGNOSIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                 |

|                      | 2.1 Introduction 2.2 Diagnostic Guides 2.2.1 FAIL 1 (Excessive internal Temperature) 2.2.2 FAIL 2 (Over-Voltage) 2.2.3 FAIL 3 (Control Data Corrupted) 2.2.4 FAIL 4 (Precision Divider Fault) 2.2.5 FAIL 5 (Safety Circuits 'Watchdog' Tripped) 2.2.6 FAIL 6 (Calibration Memory Fault) 2.2.7 FAIL 7 (P. A. 400V Power Failure) 2.2.8 FAIL 8 (P. A. 38V Power Failure) 2.2.9 FAIL 9 (P. A. 15V Power Failure) 2.2.10 Error EF (External Frequency selected but not detected) 2.2.11 Error OL (Output Limits exceeded) 2.3 Self-Test Sequence | . 2-2<br>. 2-2<br>. 2-3<br>. 2-3<br>. 2-4<br>. 2-5<br>. 2-5<br>. 2-6<br>. 2-7<br>. 2-8<br>. 2-9 |

|                      | DISMANTLING AND REASSEMBLY  1.1 General Precautions 1.2 General Mechanical Layout 1.3 Location and Access 1.4 General Access                                                                                                                                                                                                                                                                                                                                                                                                                 | . 3-1<br>. 3-2<br>. 3-3                                                                         |

|                      | BERVICING AND INTERNAL ADJUSTMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 3-5                                                                                           |

|                      | . 1 Introduction . 2 Cleaning the Air Intake Filter . 3 Lithium Battery - Replacement . 4 Ohms Function - Standard Resistor Adjustment . 5 Bias Current Adjustment - 100V PA . 6 Capacitive Load Test . 7 Quiescent Current Adjustment - Current/Ohms Assembly . 8 Compliance Adjustment - Current/Ohms Assembly . 9 Common Mode Null Adjustments                                                                                                                                                                                            | . 4-3<br>. 4-4<br>. 4-6<br>. 4-6<br>. 4-7<br>. 4-8<br>. 4-9                                     |

#### PART 2 TECHNICAL DESCRIPTIONS

| Sect | tion   | Title                                               | Page |

|------|--------|-----------------------------------------------------|------|

| 5    | PRINC  | CIPLES OF OPERATION                                 |      |

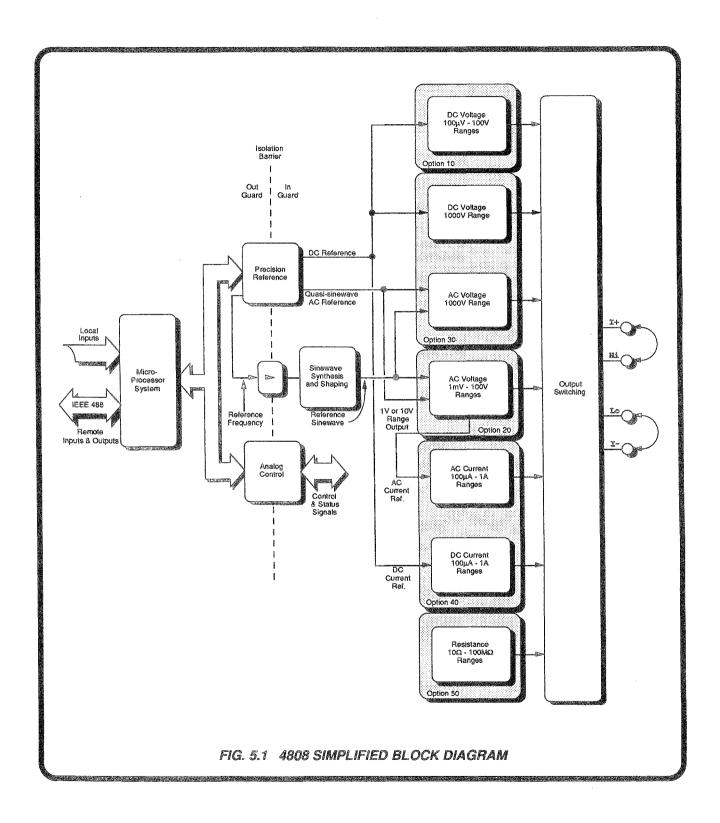

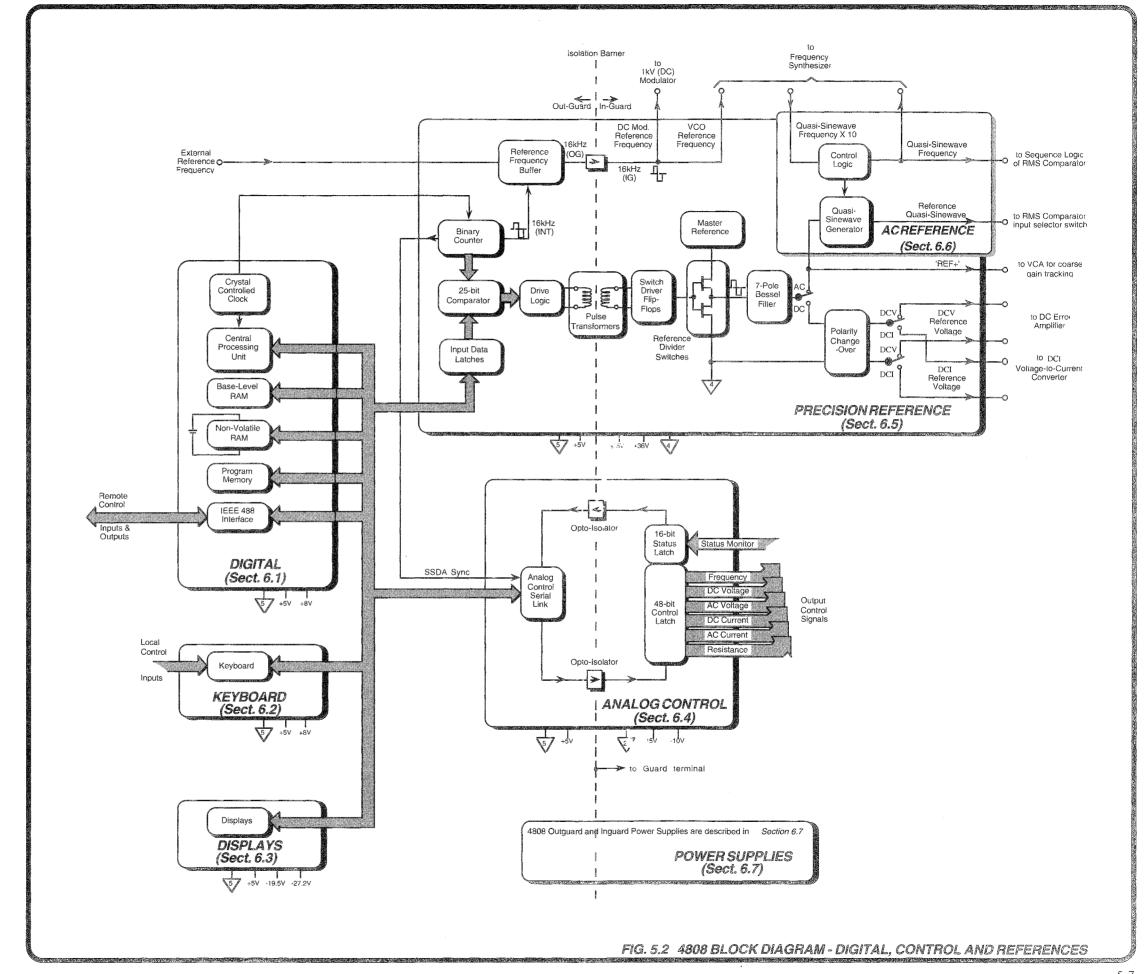

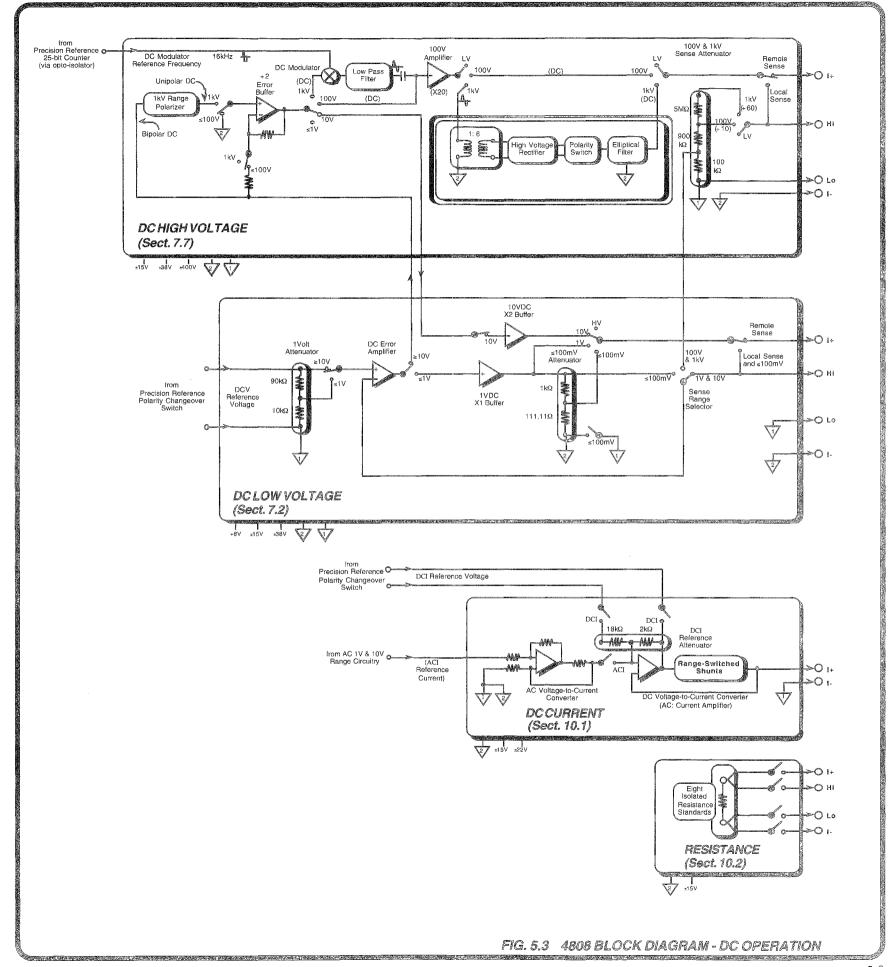

|      | 5.1    | Block Diagrams                                      | 5-1  |

|      |        | Inputs                                              |      |

|      | 5.3    | Digital Outputs                                     | 5-1  |

|      | 5.4    | Precision Reference                                 | 5-2  |

|      |        | Analog Control                                      |      |

|      | 5.6    | DC Voltage Outputs                                  | 5-3  |

|      |        | AC Voltage Outputs                                  |      |

|      |        | 1000V Ranges                                        |      |

|      |        | DC/AC Current Outputs                               |      |

| •    |        | Resistance Outputs                                  |      |

|      |        | Datron 'Autocal'                                    |      |

| 6    | DIGITA | AL CIRCUITS; REFERENCE CIRCUITS; POWER SUPPLIE      | S    |

|      | 6.1    | Digital                                             | 6-1  |

|      |        | Keyboard                                            |      |

|      |        | Digital Displays                                    |      |

|      |        | Analog Control Interface                            |      |

|      |        | Precision Divider                                   |      |

|      |        | AC Reference - the Quasi-Sinewave                   |      |

|      | 6.7    | Power Supplies                                      | 6-47 |

| 7    | DC VC  | OLTAGE OUTPUTS - AMPLITUDE CONTROL SYSTEM           |      |

|      | 7.1    | Introduction                                        | 7-1  |

|      | 7.2    | Low Voltage Loops                                   |      |

|      | 7.3    | .DC 1V Loop                                         |      |

|      |        | . 100mV Range                                       |      |

|      |        | . 100µV - 10mV Ranges                               |      |

|      |        | .DC 10V Loop                                        |      |

|      | 7.7    | .DC High Voltage Loops                              |      |

|      | 7.8    | . 100V Range                                        | 7-10 |

|      | 7.9    | . 1000V Range                                       | 7-15 |

|      | 7.10   | Logic Control of DC Outputs                         |      |

|      | 7.11   | .DC Assembly Relay Drives and Logic                 | 7-2  |

|      |        | PA Assembly Logic and Relay Drives                  |      |

| 8    | AC V   | OLTAGE OUTPUTS - FREQUENCY CONTROL SYSTEM           |      |

|      | 8.1    | . Digital Frequency Synthesizer                     | 8-1  |

|      | 8.2    | . Quadrature Sinewave Oscillator                    | 8-9  |

|      |        | External Frequency Lock                             |      |

| 9    | AC V   | OLTAGE OUTPUTS - AMPLITUDE CONTROL SYSTEM           |      |

|      | 9.1    | . Introduction                                      | 9-1  |

|      |        | AC Voltage Amplitude Control System - Block Diagram |      |

|      |        | . Voltage Controlled Amplifiers                     |      |

|      |        | .AC Low Voltage Loop                                |      |

|      |        | .AC High Voltage Loops                              |      |

|      | 9.6    | AC 100V Range                                       | 9-13 |

|      |        | .AC 1000V Range                                     |      |

|      |        | .AC High Voltage Sensing                            |      |

|      |        | .Sine/Quasi-Sine RMS Comparator                     |      |

|      | 9.10   | Logic Control of AC Outputs                         | 9-30 |

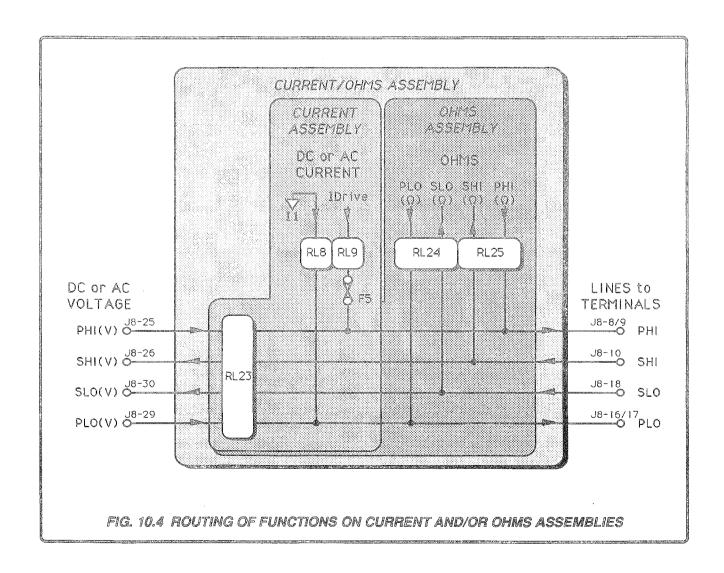

#### 10 CURRENT OUTPUTS AND RESISTANCE

| 10.1 DC and AC Current                           | 10-1 |

|--------------------------------------------------|------|

| 10.2 Resistance                                  | 10-5 |

| 10.3 Function Switching                          | 10-6 |

| 10.4 Current and/or Ohms Assembly Analog Control |      |

#### **ILLUSTRATIONS**

#### PART 1 CALIBRATION AND SERVICING INFORMATION

| Se | ection Title                                                                                                          | Page |

|----|-----------------------------------------------------------------------------------------------------------------------|------|

| 1  | CALIBRATION                                                                                                           |      |

|    | Preparing/Returning to Use: IEEE 488 and Security Keyswitch Settings                                                  | 1-3  |

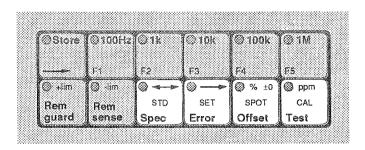

|    | Autocal Facilities: Autocal Keys                                                                                      | 1-5  |

|    | Remote Calibration Guidelines: Transfer of Calibration Facilities                                                     | 1-7  |

| •  | Pre-Calibration: Identification of Access Holes                                                                       | 1-9  |

|    | Procedure: DCV Pre-cal ConnectionsACV LF Pre-cal Connections                                                          |      |

|    | ACV HF Pre-cal Connections Pre-Cal Disable                                                                            |      |

|    | Remote Pre-Calibration Guidlines: Transfer of DC Pre-Calibration Facilities Transfer of AC Pre-Calibration Facilities |      |

| 2  | FAULT DIAGNOSIS                                                                                                       |      |

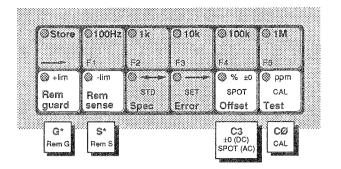

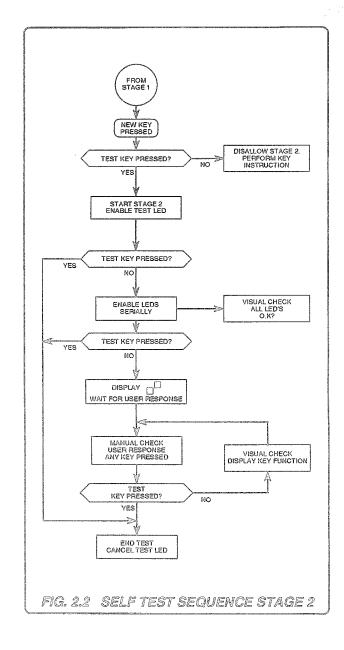

| ٠  | Self Test Sequence: Stage 1 Stage 2                                                                                   |      |

| 3  | DISMANTLING AND REASSEMBLY                                                                                            |      |

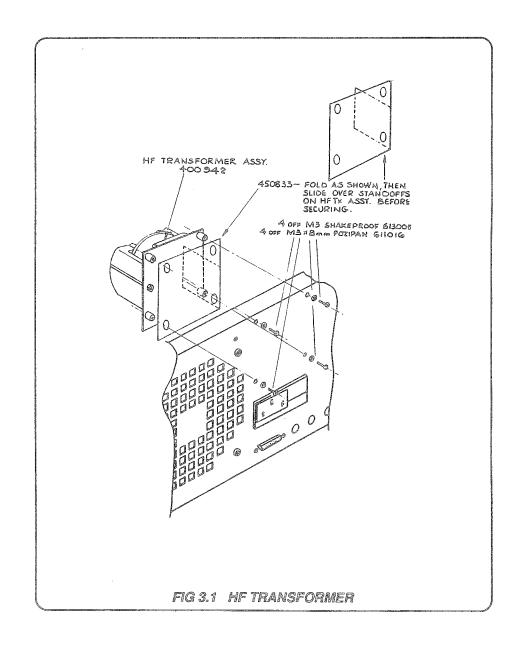

|    | HF Transformer Assembly: HF Transformer                                                                               | 3-10 |

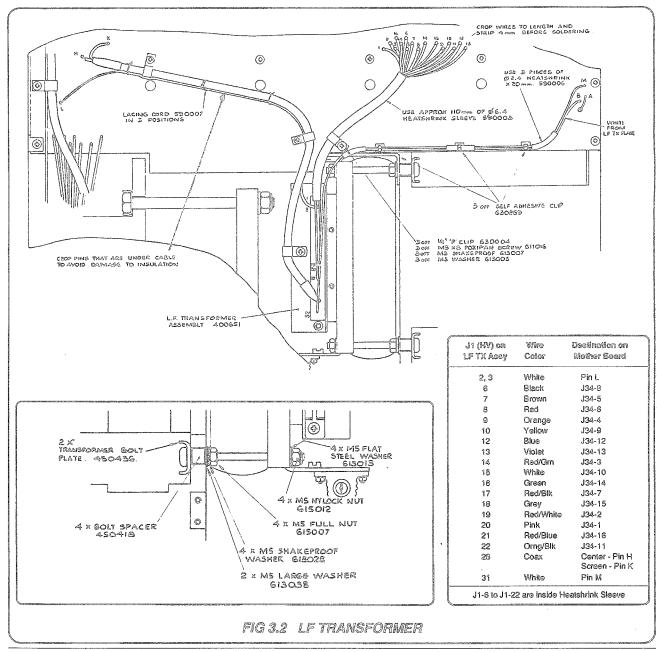

|    | LF Transformer Assembly: LF Transformer                                                                               | 3-11 |

| 4  | SERVICING AND INTERNAL ADJUSTMENTS                                                                                    |      |

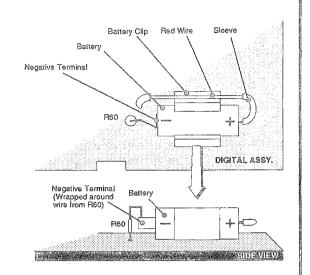

|    | Battery Replacement                                                                                                   | 4-5  |

#### PART 2 TECHNICAL DESCRIPTIONS

| Section | Figure | Title                                                        | •                                       | Page  |

|---------|--------|--------------------------------------------------------------|-----------------------------------------|-------|

| 5       | 5.1    | 4808 Simplified Block Diagram                                |                                         | 5-0   |

|         |        | 4808 Block Diagram - Digital, Control and References         |                                         |       |

|         | 5.3    | 4808 Block Diagram - DC Operation                            |                                         | . 5-9 |

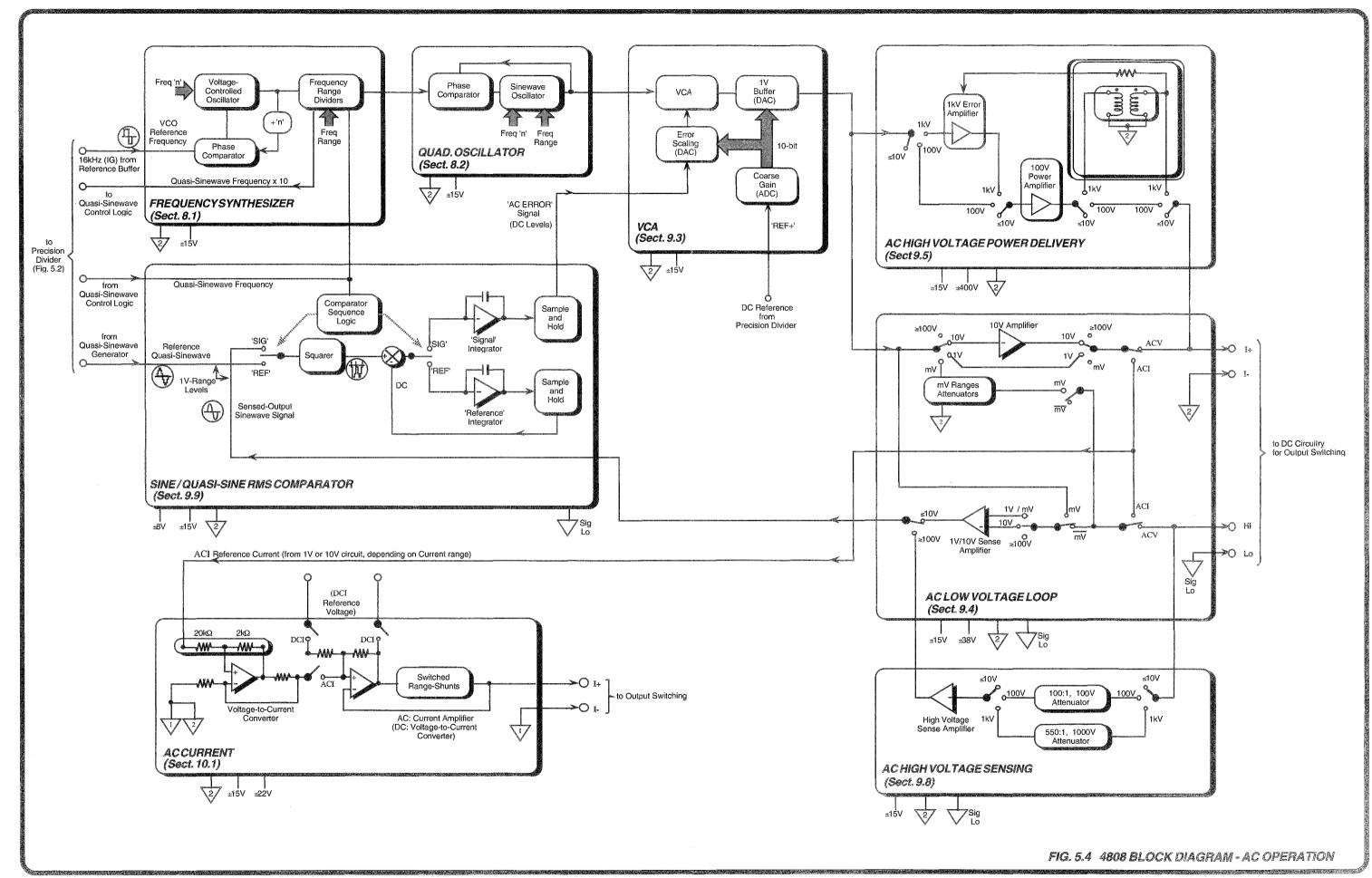

|         | 5.4    | 4808 Block Diagram - AC Operation                            |                                         | 5-11  |

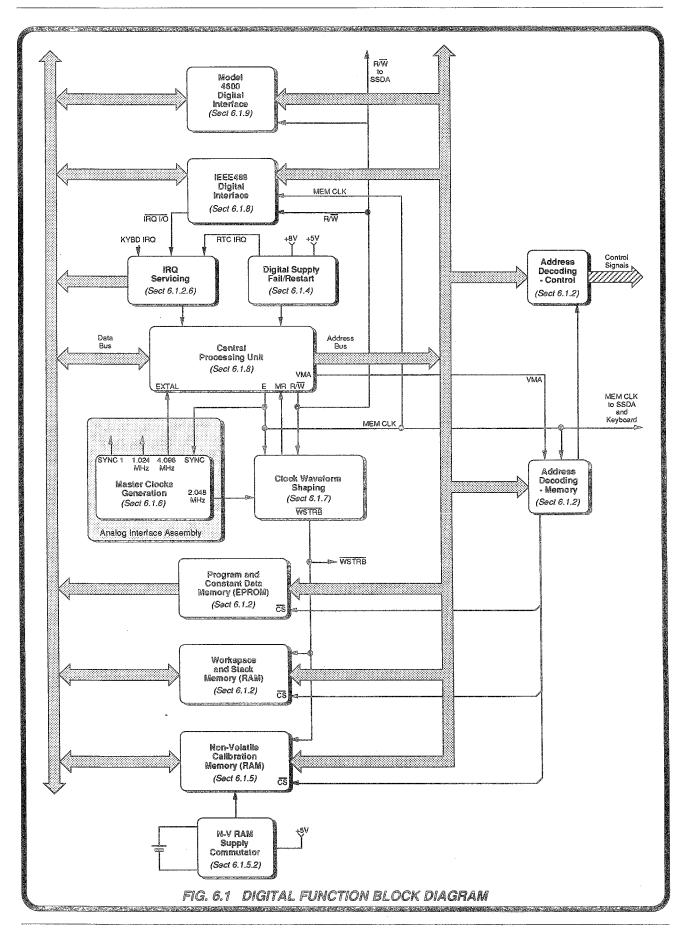

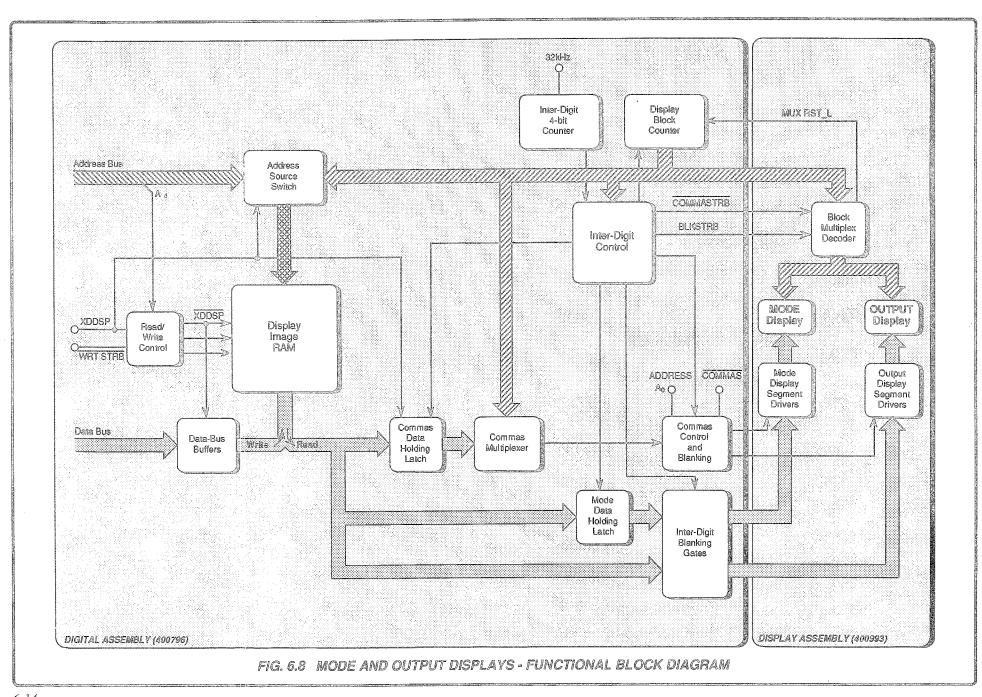

| 6       |        | . Digital Function Block Diagram                             |                                         |       |

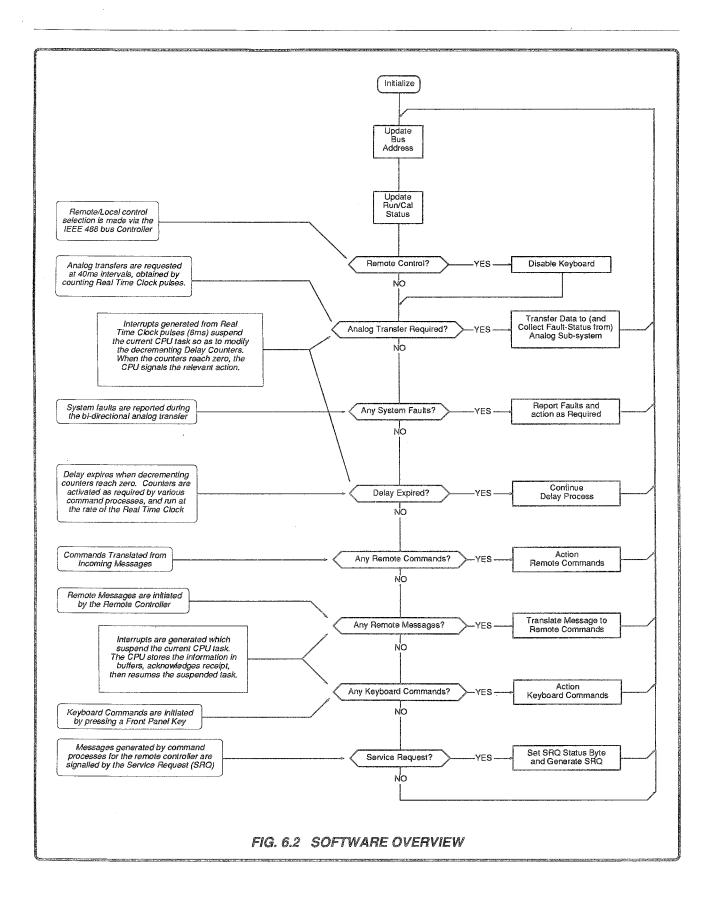

| •       |        | Software Overview                                            |                                         |       |

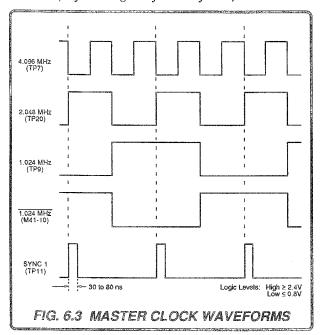

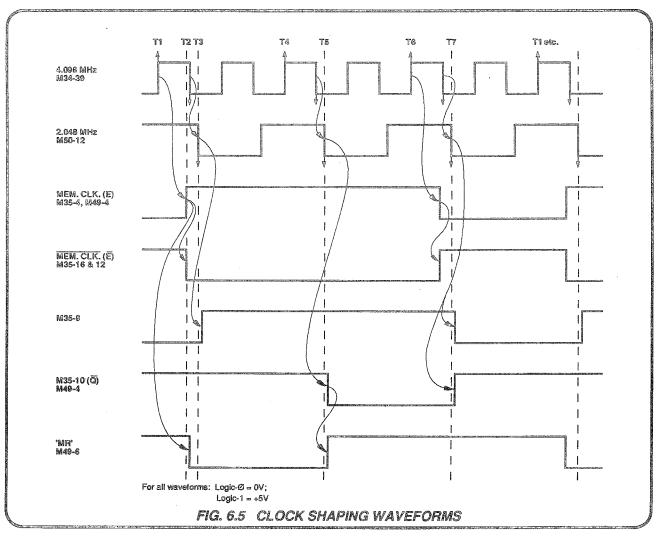

|         |        | Master Clock Waveforms                                       |                                         |       |

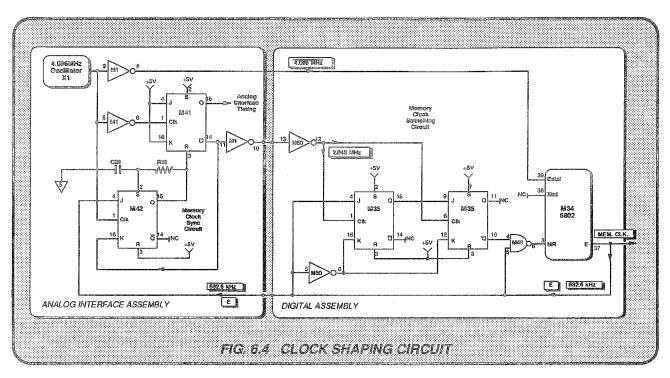

|         |        | Clock Shaping Circuit                                        |                                         |       |

|         |        | Clock Shaping Gircuit                                        |                                         |       |

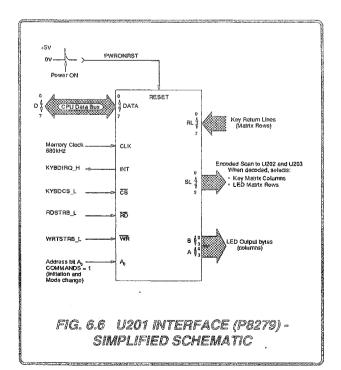

|         |        | U201 Interface (P8279) - Simplified Schematic                |                                         |       |

|         |        |                                                              |                                         |       |

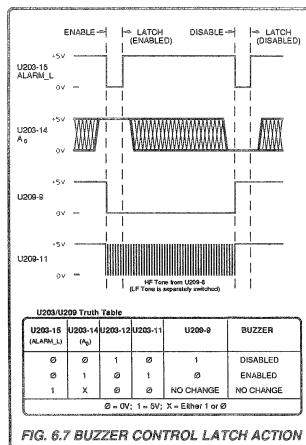

|         |        | Buzzer Control Latch Action                                  |                                         |       |

|         |        |                                                              |                                         |       |

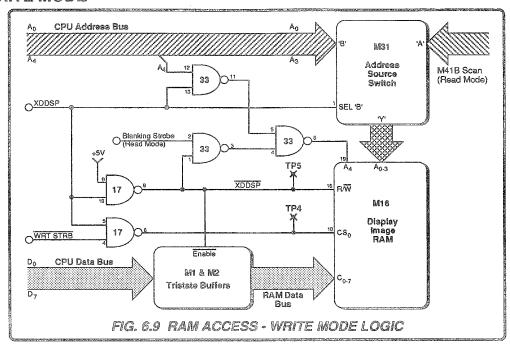

|         |        | RAM Access - Write Mode Logic                                |                                         |       |

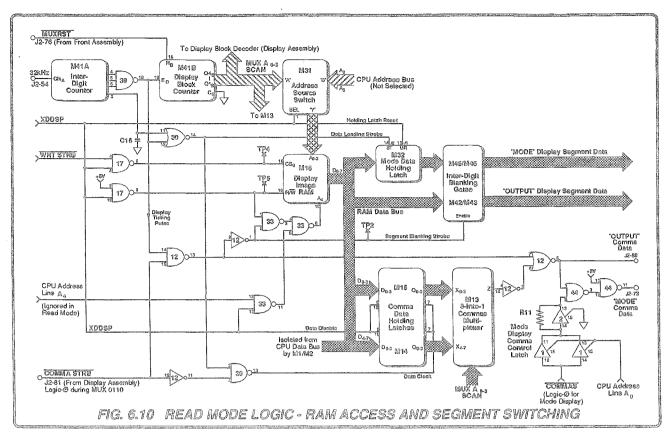

|         |        | Read Mode Logic - RAM Access and Segment Switching .         |                                         |       |

|         |        | Display Scan Sequences                                       |                                         |       |

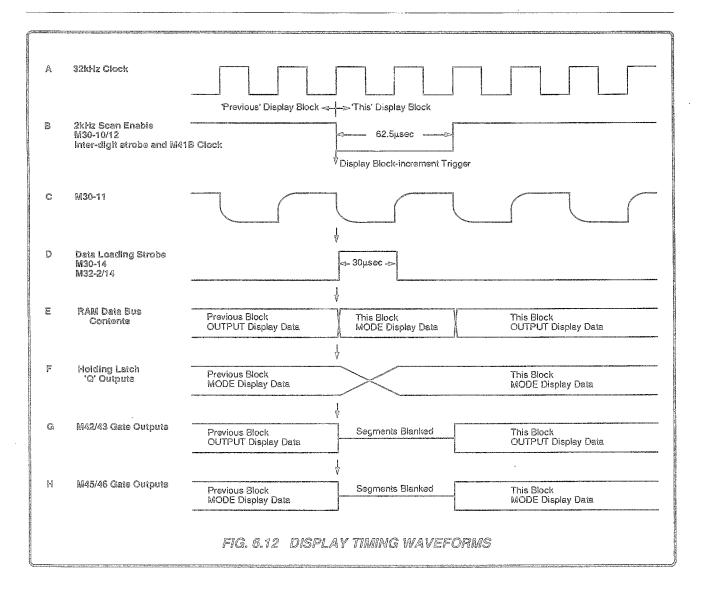

|         |        | Display Timing Waveforms                                     |                                         |       |

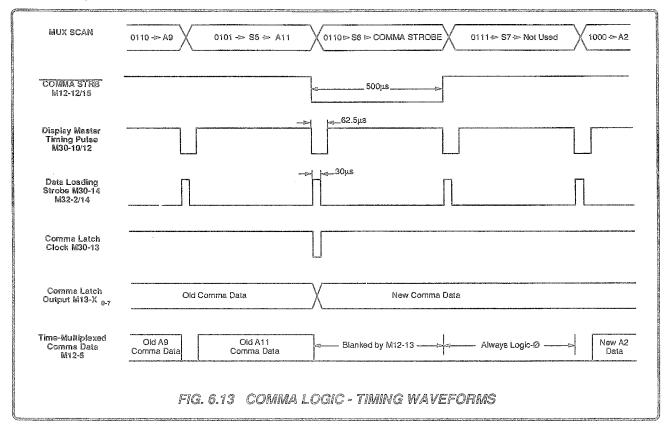

|         |        | Comma Logic - Timing Waveforms                               |                                         |       |

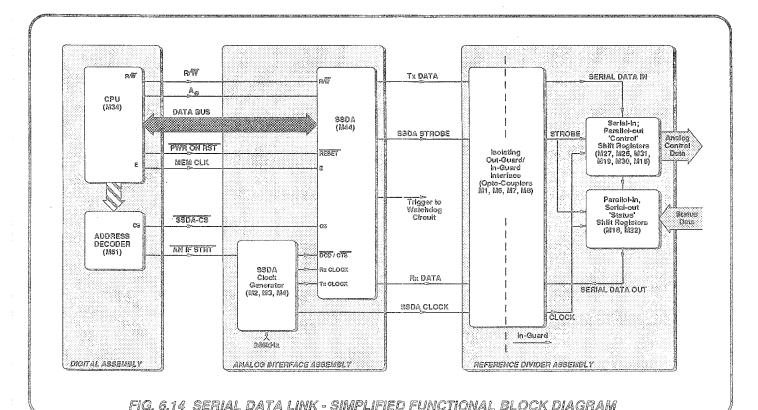

|         |        | Serial Data Link - Simplified Functional Block Diagram       |                                         |       |

|         |        | Serial Data Transfer Organization                            |                                         |       |

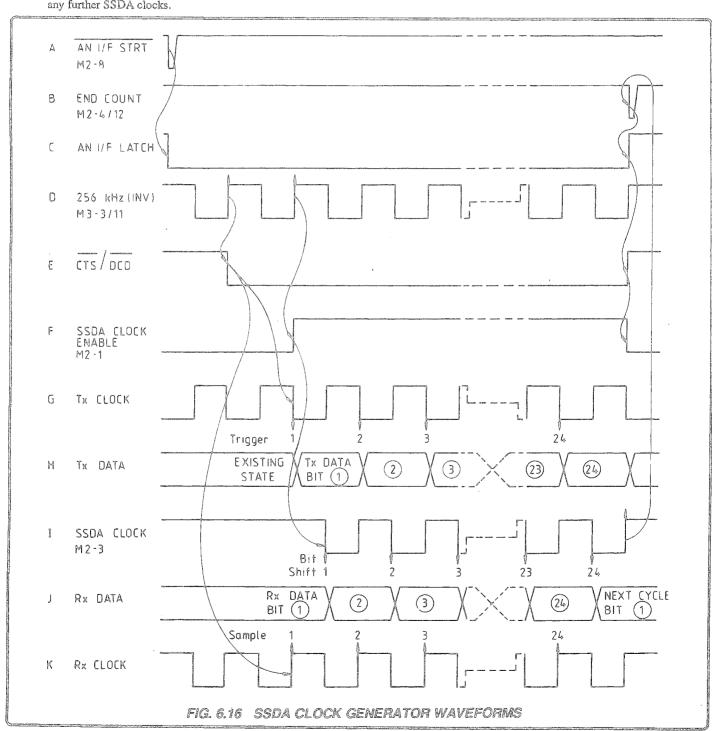

|         |        | SSDA Clock Generator Waveforms                               |                                         |       |

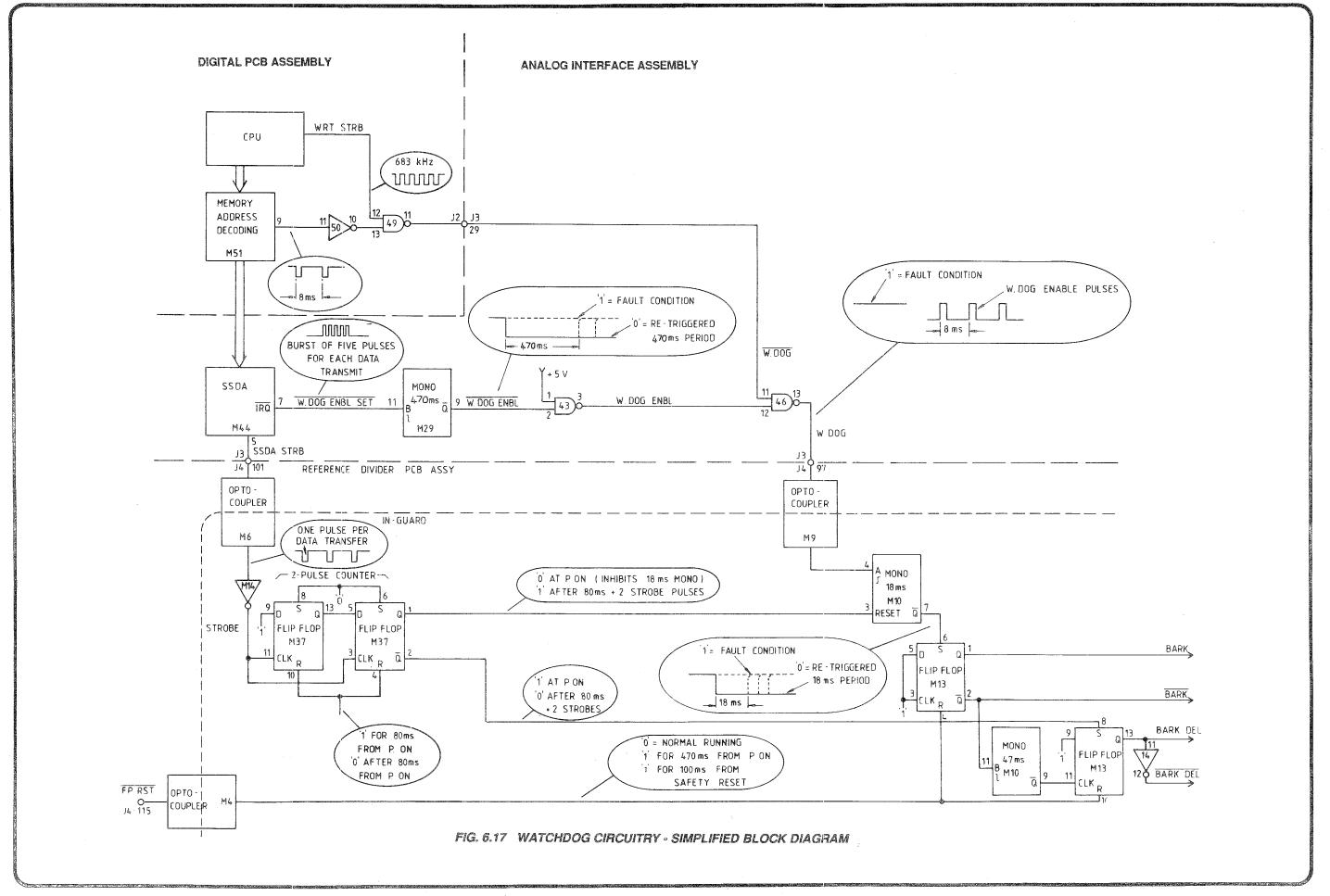

|         |        | WATCHDOG Circuitry - Simplified Block Diagram                |                                         |       |

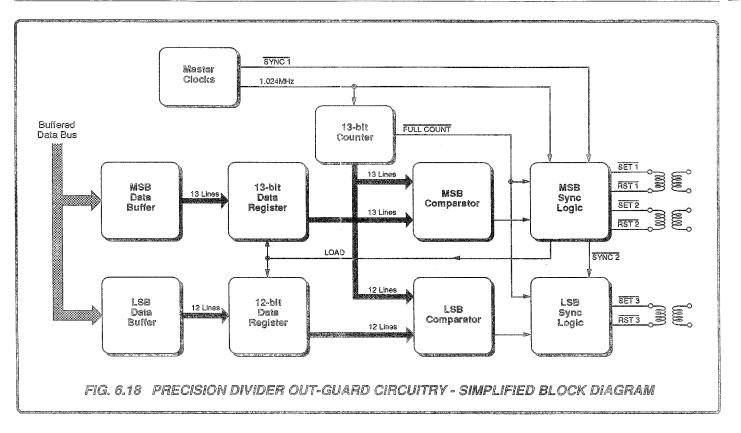

|         |        | Precision Divider Out-Guard Circuitry - Simplified Block Dia |                                         |       |

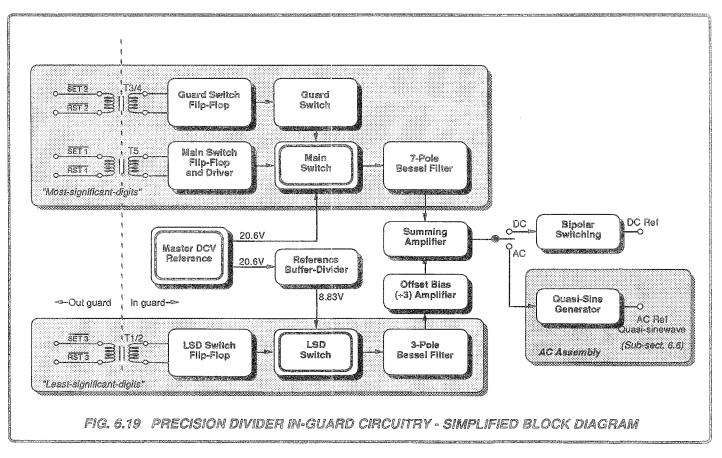

|         | 6.19   | Precision Divider In-Guard Circuitry - Simplified Block Diag | jram                                    | 6-30  |

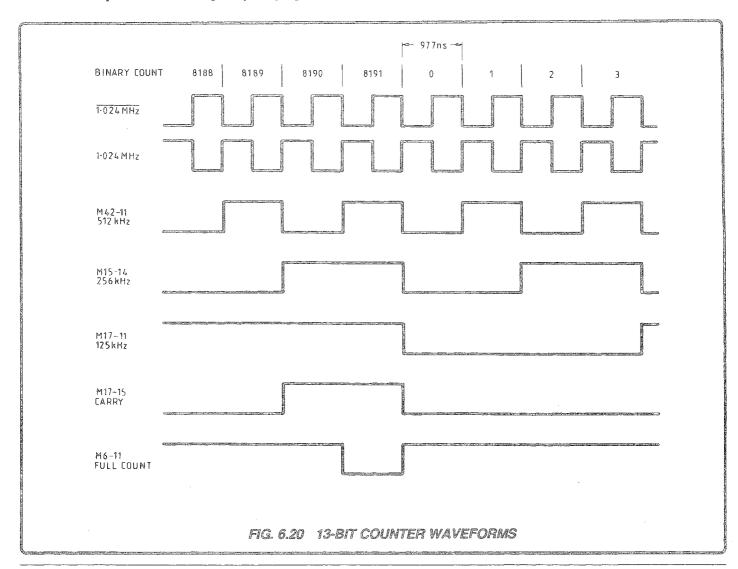

|         | 6.20   | 13-Bit Counter Waveforms                                     |                                         | 6-32  |

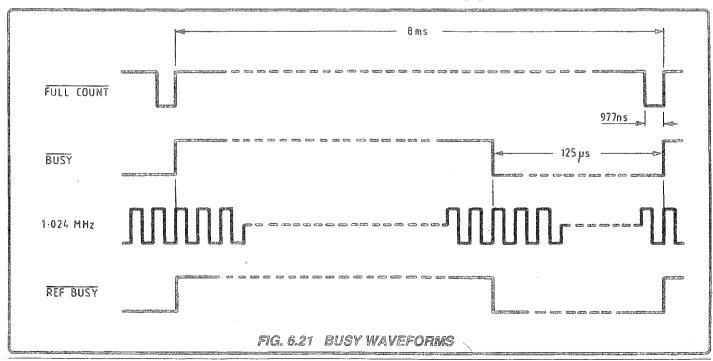

|         | 6.21   | BUSY Waveforms                                               |                                         | 6-33  |

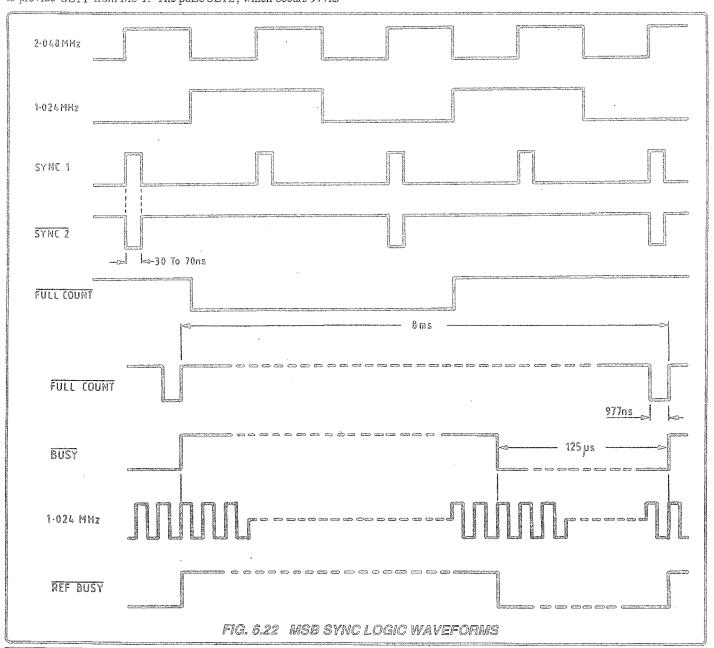

|         | 6.22   | MSB Sync Logic Waveforms                                     |                                         | 6-34  |

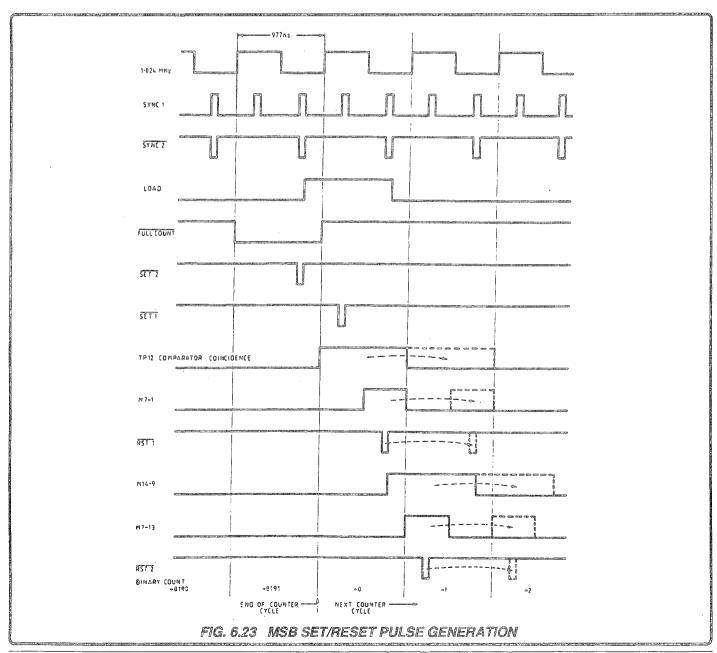

|         | 6.23   | MSB Set/Reset Pulse Generation                               |                                         | 6-35  |

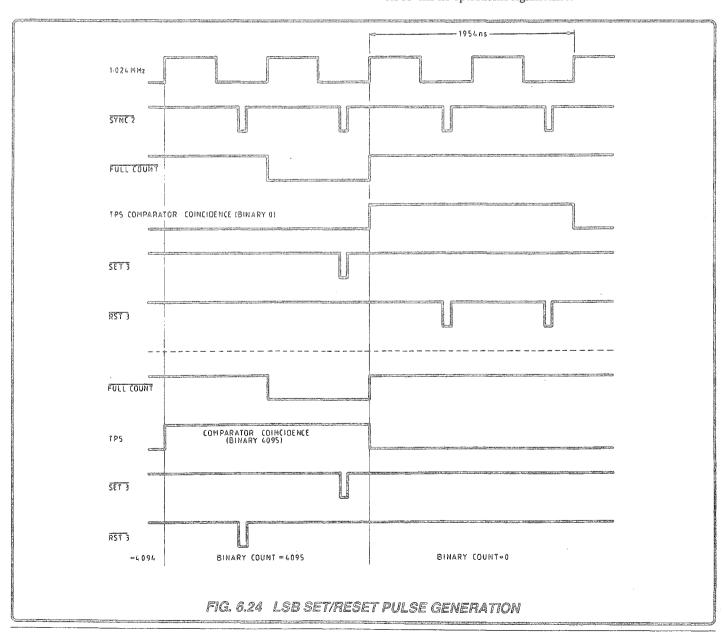

|         |        | LSB Set/Reset Pulse Generation                               |                                         |       |

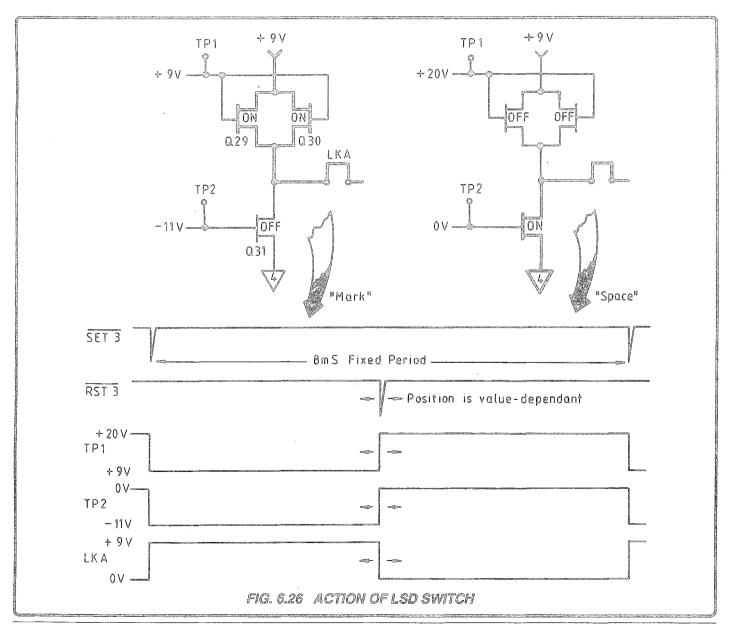

|         | 6.26   | Action of LSD Switch                                         |                                         | 6-38  |

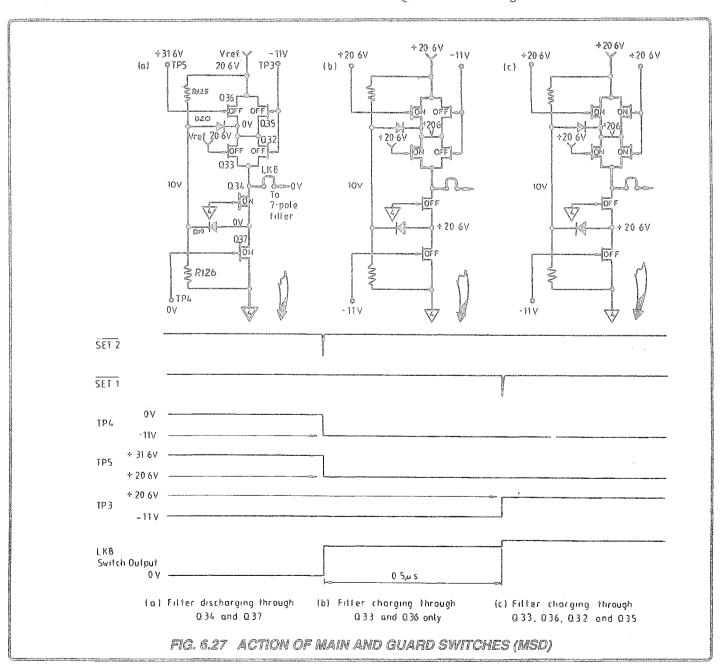

|         | 6.27   | Action of Main and Guard Switches (MSD)                      |                                         | 6-40  |

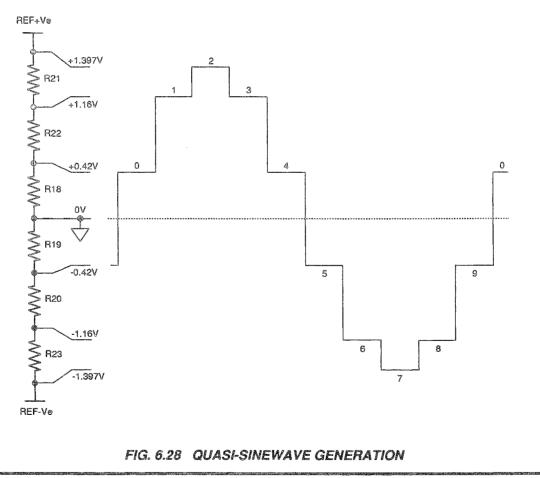

|         |        | Quasi-Sinewave Generation                                    |                                         |       |

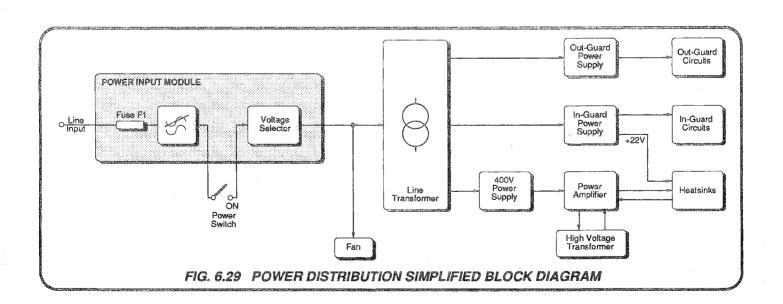

|         |        | Power Distribution Simplified Block Diagram                  |                                         |       |

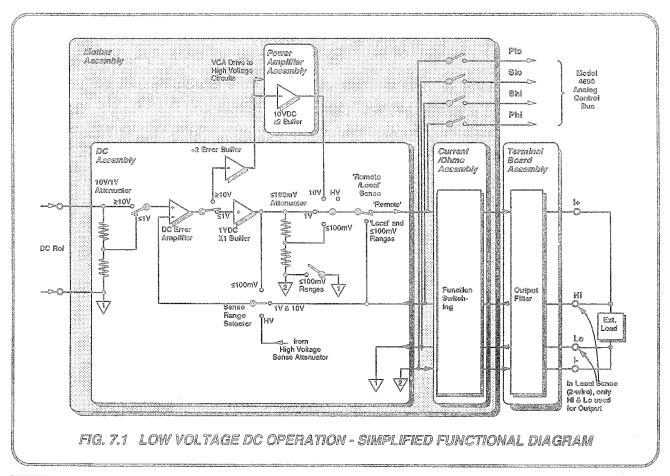

| 7       |        | Low Voltage DC Operation - Simplified Functional Diagram     |                                         |       |

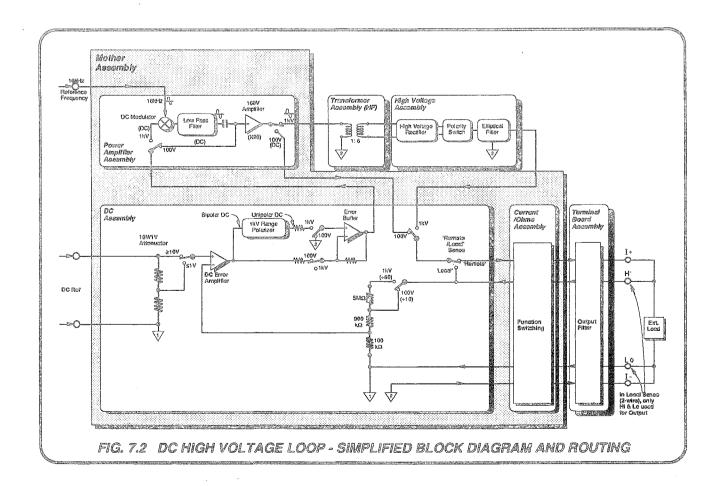

| •       | 7.9    | DC High Voltage Loop - Simplified Block Diagram and Rou      | 191000                                  | 70    |

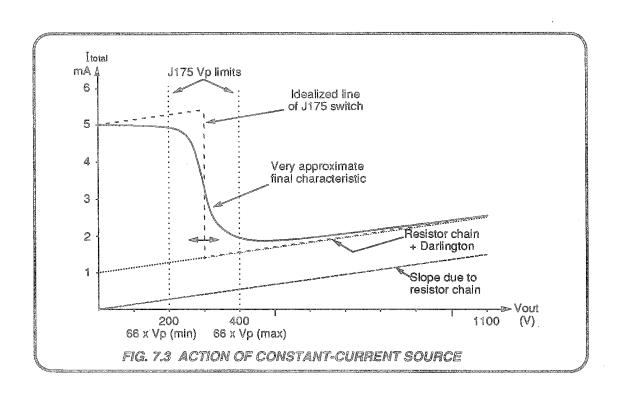

|         |        | Action of Constant-Current Source                            |                                         |       |

|         |        |                                                              |                                         |       |

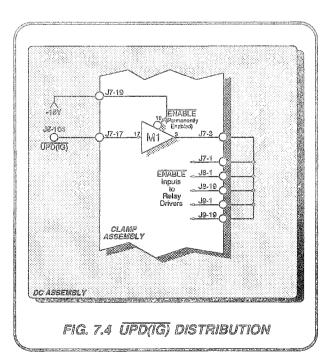

|         | 7.4    | UPD(IG) Signal Distribution                                  |                                         | 7-21  |

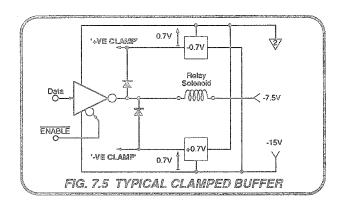

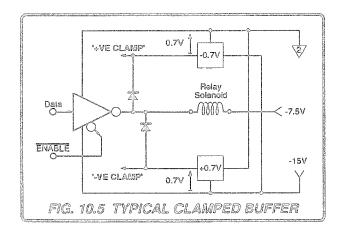

|         | 7.5    | Typical Clamped Buffer                                       |                                         | 7-22  |

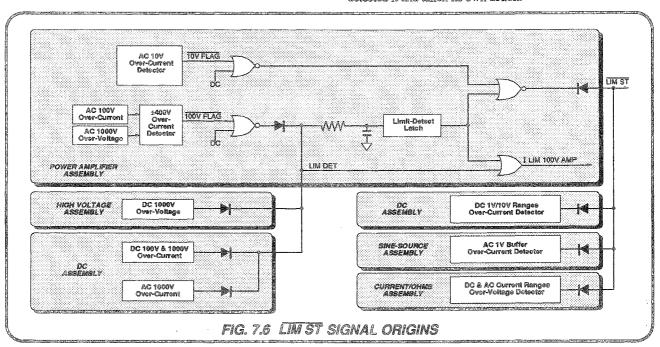

|         | 7.6    | Limit Status Signal Origins                                  |                                         | 7-25  |

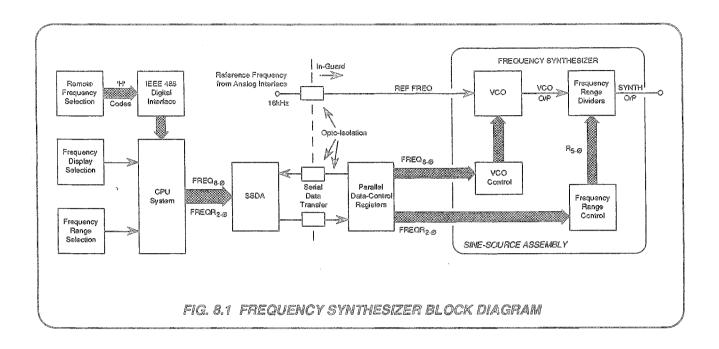

| 8       | 8.1    | Frequency Synthesizer Block Diagram                          |                                         | 8-1   |

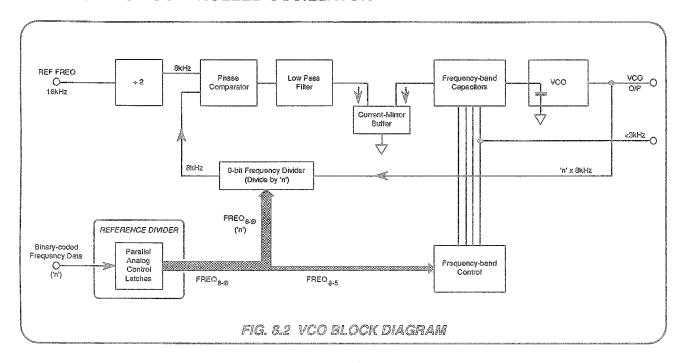

|         |        | VCO Block Diagram                                            |                                         |       |

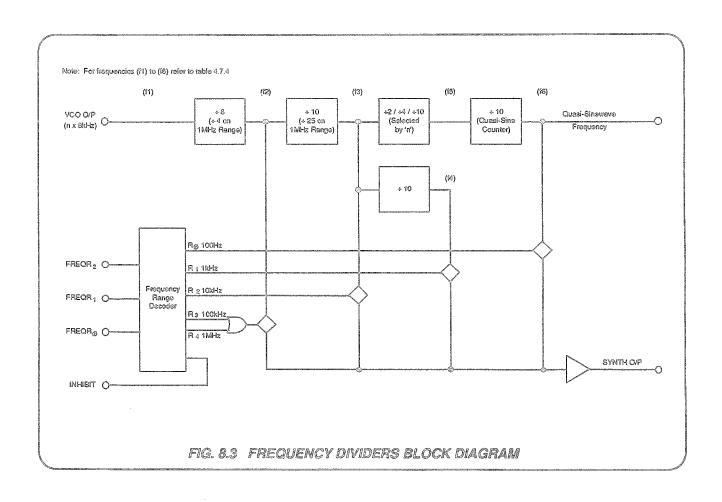

|         | 8.3    | Frequency Dividers Block Diagram                             |                                         | 8-4   |

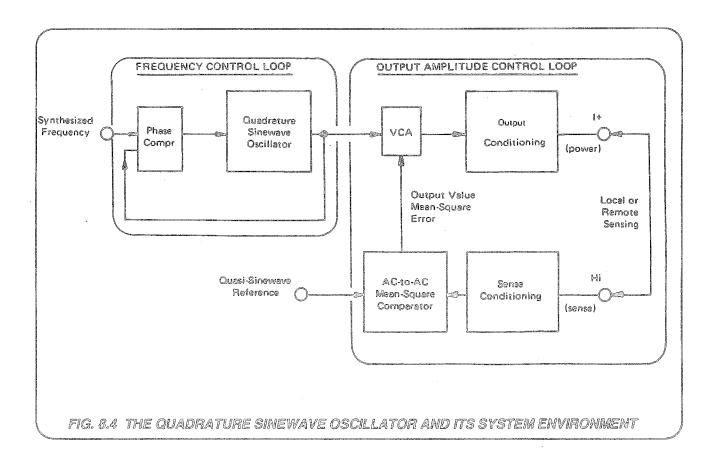

|         | 8.4    | The Quadrature Sinewave Oscillator and its System Enviro     | nmeni                                   | 8-9   |

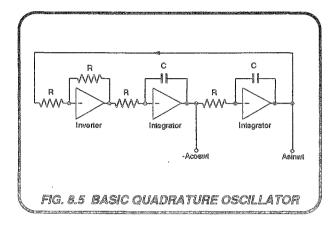

|         |        | Basic Quadrature Sinewave Oscillator                         |                                         |       |

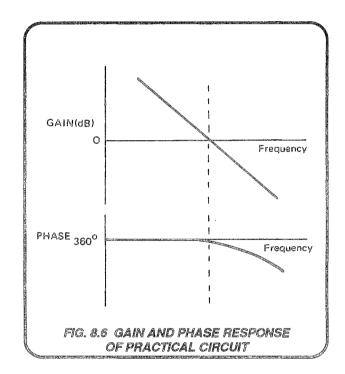

|         |        | Gain and Phase Response of Practical Circuit                 |                                         |       |

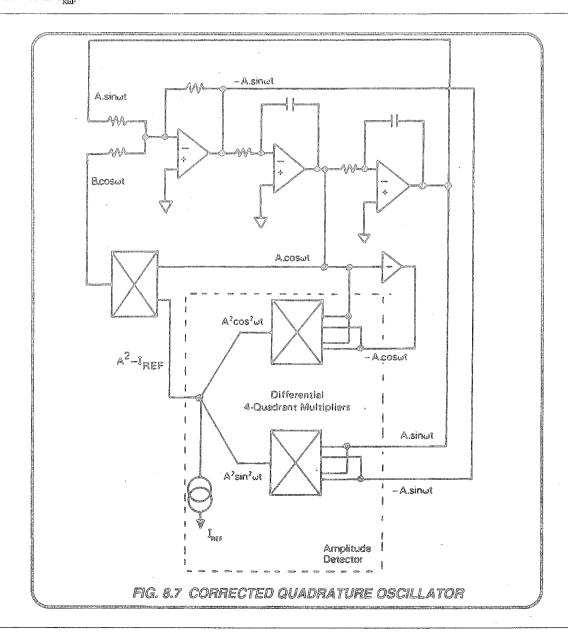

|         |        | . Corrected Quadrature Oscillator                            |                                         |       |

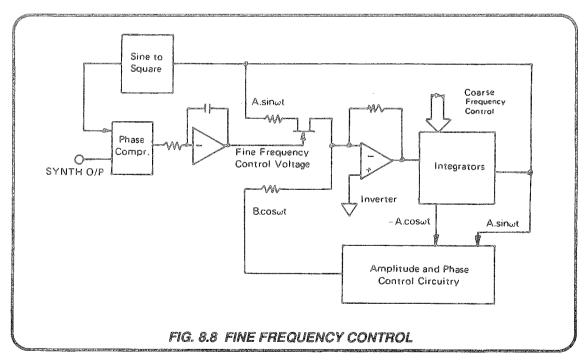

|         | 8.8    | Fine Frequency Control                                       | *************************************** | 8-12  |

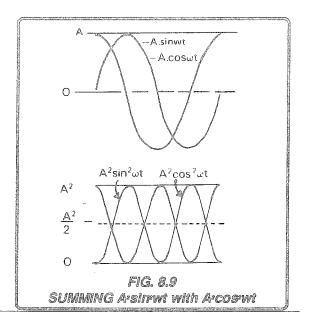

|         | 8.9    | Summing A²sin²wt with A²cos²wt                               | ••••••••••••••••••••••••••••••••••••••• | 8_1/  |

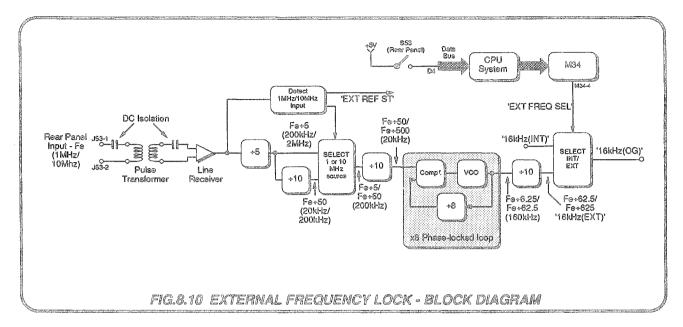

|         |        | External Frequency Lock - Block Diagram                      |                                         |       |

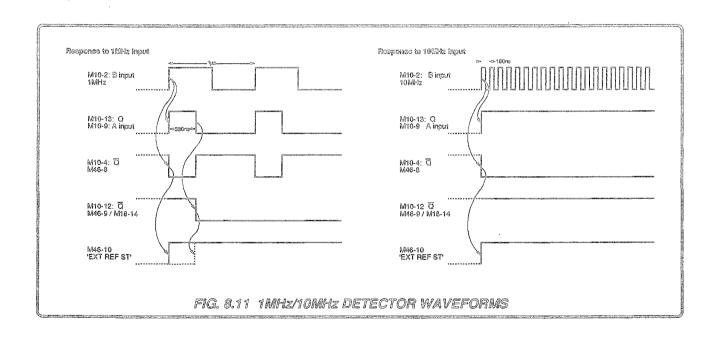

|         | 8-11   | 1MHz/10MHz Detector Waveforms                                | *************************************** | 0-17  |

| 9       | 0 11   | Output Amelitude Control Custom                              | *************************************** | 0-10  |

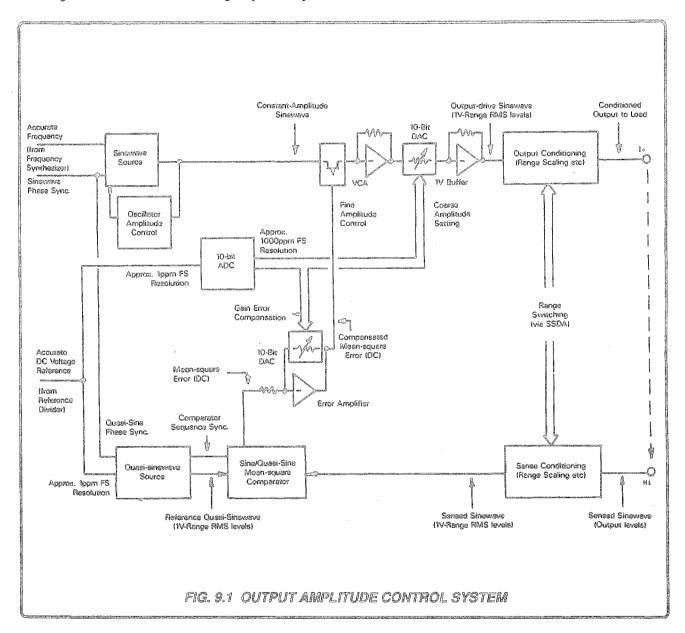

| 3       | 9.1    | Output Amplitude Control System                              |                                         | 9-1   |

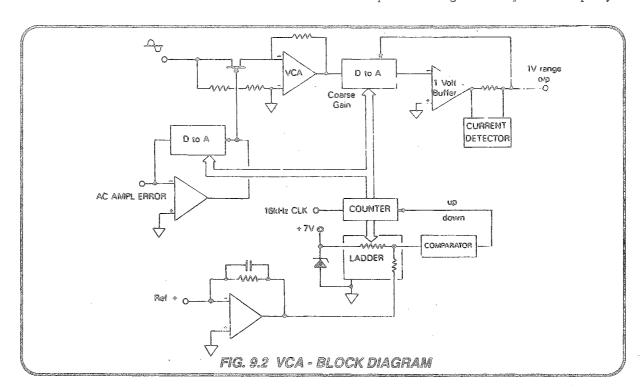

|         | 9.2    | VCA - Block Diagram                                          |                                         | 9-3   |

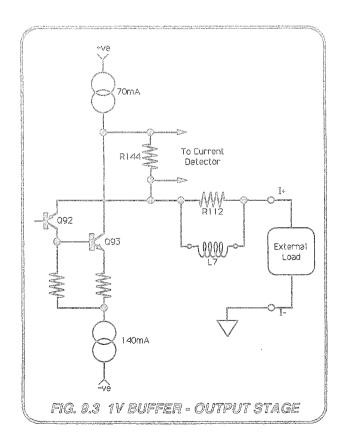

|         | 9.3    | 1V Buffer - Output Stage                                     |                                         | 9-4   |

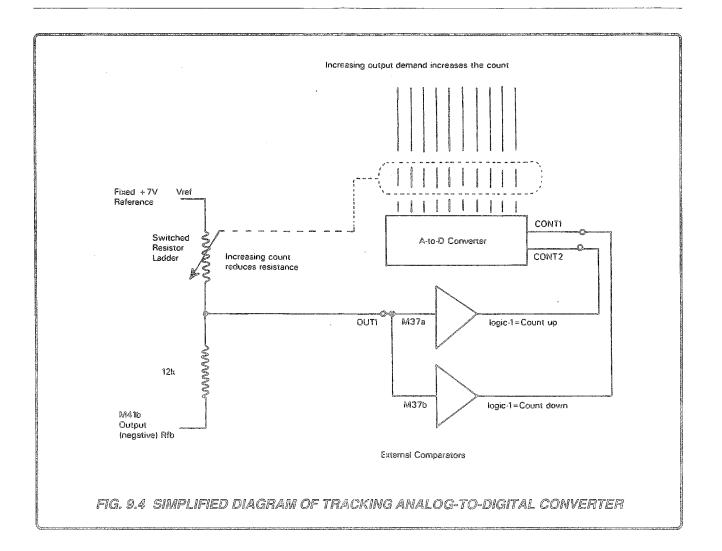

|         | 9.4    | Simplified Diagram of Tracking Analog-to-Digital Converter   | ·                                       | 9-5   |

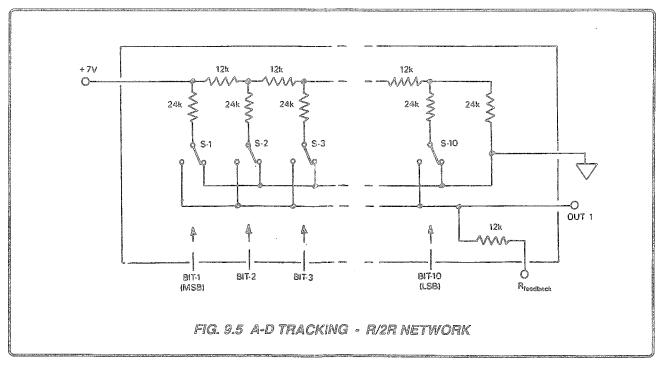

|         | 9.5    | A-D Tracking - R/2R Network                                  |                                         | 9-5   |

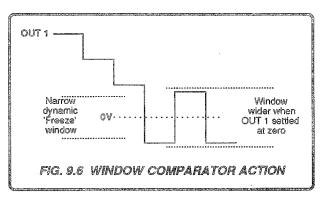

|         | 9.6    | Window Comparator Action                                     |                                         | 9-6   |

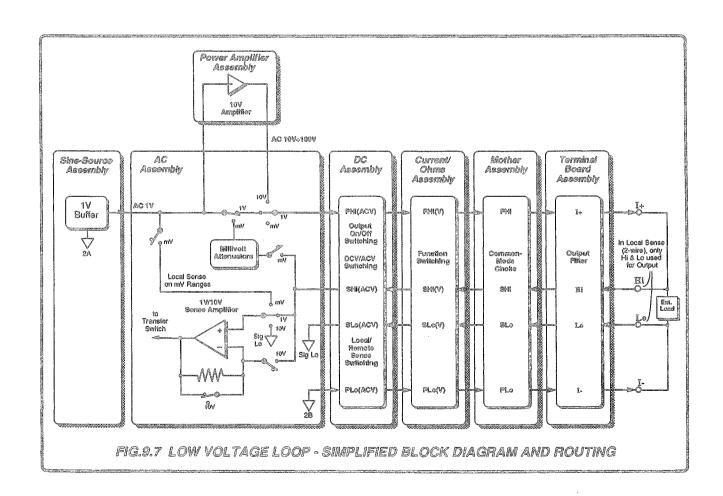

|         | 9.7    | Low Voltage Loop - Simplified Block Diagram and Routing      |                                         | 9-7   |

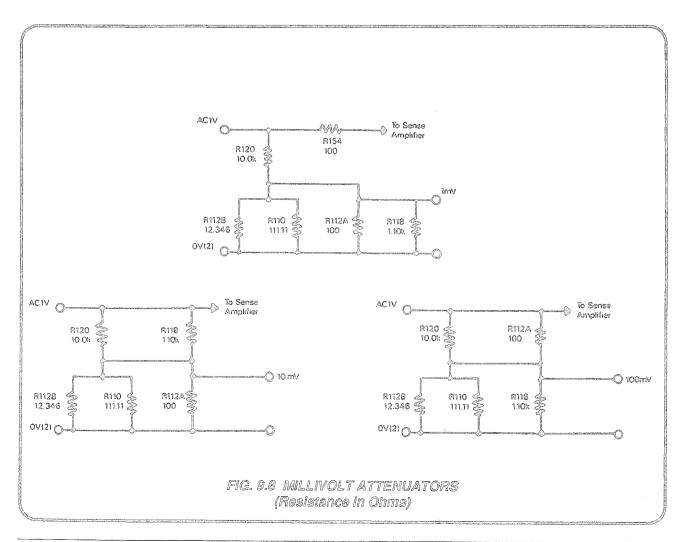

|         | 9.8    | Millivolt Attenuators                                        |                                         | 9-10  |

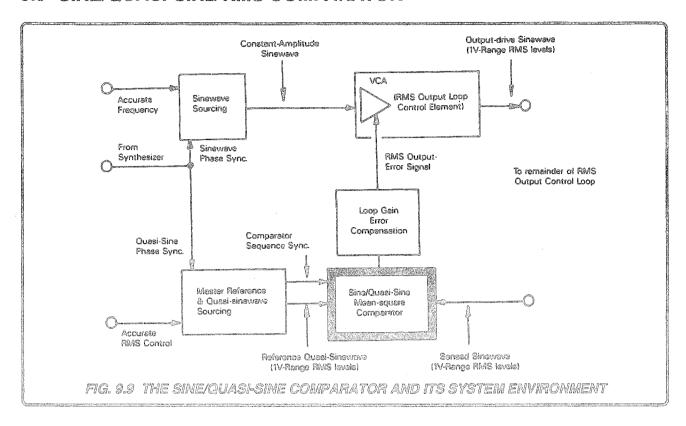

|         | 9.9    | The Sine/Quasi-Sine RMS Comparator and its System Env        | vironment                               | 9-19  |

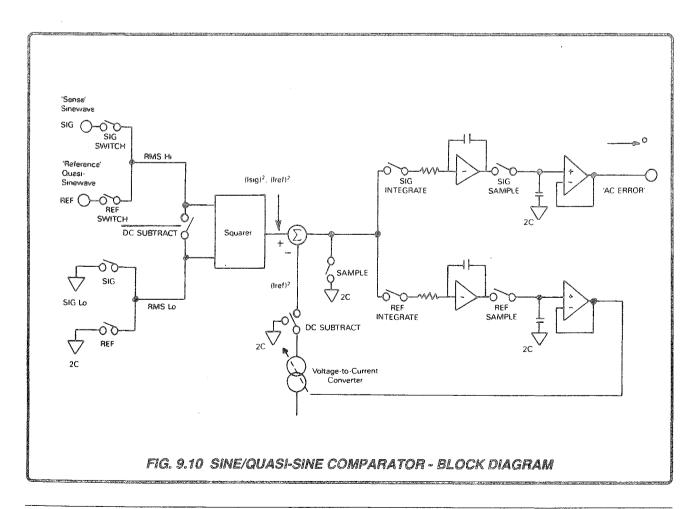

|         | 9.10   | Sine/Quasi-Sine RMS Comparator - Block Diagram               |                                         | 9-20  |

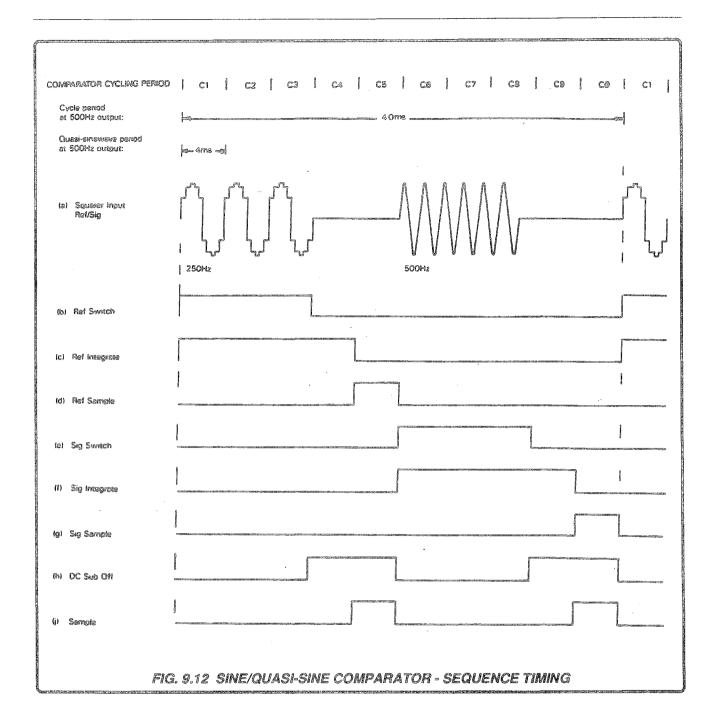

|         | 9.11   | Sine/Quasi-Sine RMS Comparator - Sequence Cycle              |                                         | 9-20  |

|         | 9.12   | Sine/Quasi-Sine RMS Comparator - Sequence Timing             | *************************************** | 9-22  |

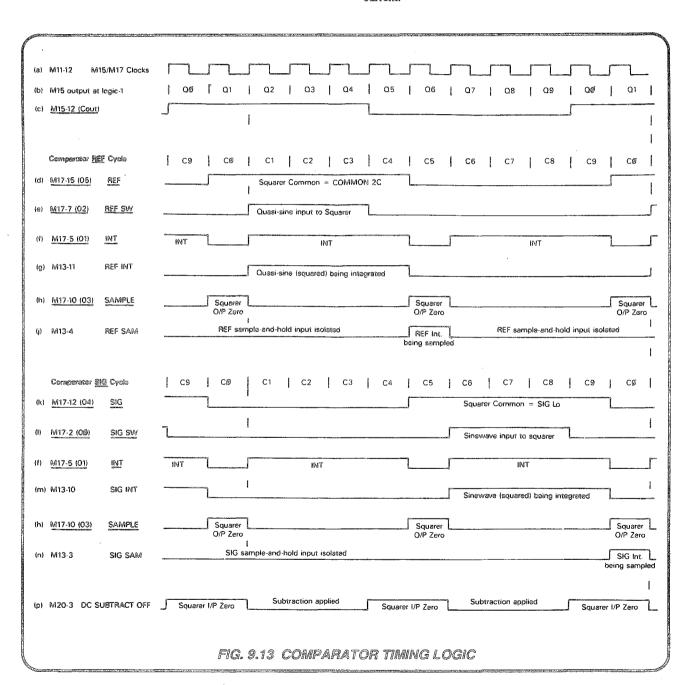

|         | 9.13   | Comparator Timing Logic                                      |                                         | 9-25  |

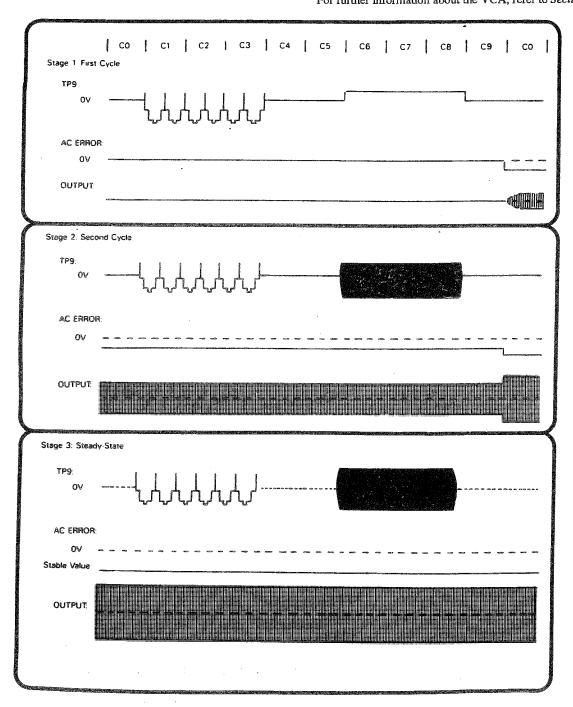

|         | 9.14   | Three Stages of Output Build-up from Zero                    |                                         | 9-29  |

| ^ -     |        |                                                              |                                         |       |

| Section | Figure | Title                                                  | Page |

|---------|--------|--------------------------------------------------------|------|

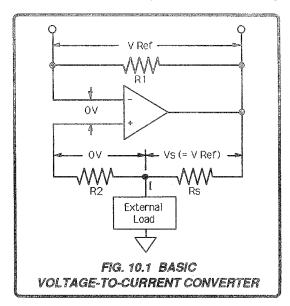

| 10      | 10.1   | Basic Voltage-to-Current Converter                     | 10-1 |

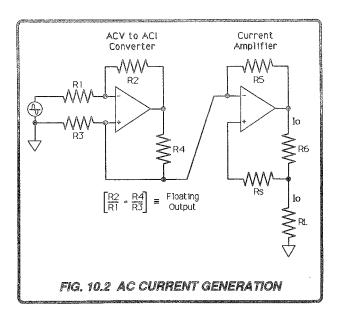

|         | 10.2   | AC Current Generation                                  | 10-1 |

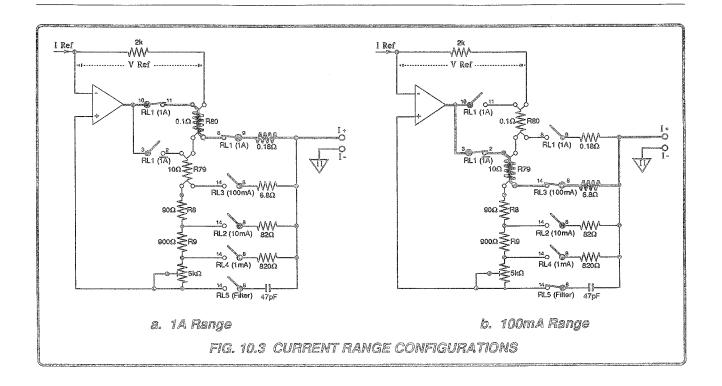

|         | 10.3   | Current Range Configurations                           | 10-3 |

|         |        | Routing of Functions on Current and/or Ohms Assemblies |      |

|         | 10.5   | . Typical Clamped Buffer                               | 10-8 |

|  |  |  | F-17-271782 1 |

|--|--|--|---------------|

|  |  |  |               |

|  |  |  |               |

|  |  |  |               |

|  |  |  |               |

|  |  |  |               |

|  |  |  |               |

|  |  |  |               |

|  |  |  |               |

|  |  |  |               |

|  |  |  |               |

|  |  |  |               |

## PART 1

## CALIBRATION AND SERVICING INFORMATION

SECTION 1 Calibration

**SECTION 2** Fault Diagnosis

SECTION 3 Dismantling and Reassembly

SECTION 4 Servicing and Internal Adjustments

|  |  | Entering of |

|--|--|-------------|

|  |  |             |

|  |  |             |

|  |  |             |

|  |  |             |

#### SECTION 1 CALIBRATION

- 1. Routine Calibration procedures are given in the *User's Handbook, Section 8*.

- 2. Users are recommended to have first completed the Verification Procedures in Section 7 of the User's Handbook.

#### 1.1 GUIDE TO CALIBRATION

#### **Circumstances Calling For Subsequent Recalibration**

#### SCHEDULED RECALIBRATION

Routine calibration is carried out from the front panel, avoiding thermal disturbance and allowing immediate return to use. The 4808 is fully calibrated before leaving the factory. The specifications for the 4808 are based on standard intervals of up to 24 hours, 90 days or 1 year from calibration. Some users will wish to maintain the highest accuracy by recalibrating at short intervals (e.g. every 24 hours). In these cases, recalibration becomes a routine task. For this reason, Routine Autocalibration procedures are given in Section 8 of the User's Handbook.

Users may wish to choose alternative schemes, accounting for:

- · The accuracy required when in use,

- The instrument specifications (User's Handbook Section 6)

- The scheduled calibration intervals normally adopted by the user's organization

The Routine Calibration procedures are sufficient for all normal recalibration purposes, except when Pre-cal is called for (*Refer to Table 1.1*).

#### RESTANDARDIZATION

Occasions may arise when it is necessary to trim the instrument's internal Master Reference. For example, when the 4808 is to be made traceable to a different National Standard, after transportation from one country to another (Refer to AUTOCAL FACILITIES page 1-5).

#### **CALIBRATION MEMORY CORRUPTION**

#### **Battery Change**

Calibration constants are stored in an internal memory which remains energized by a battery. The Lithium battery which powers the non-volatile calibration memory should be replaced after 5 years (Refer to Section 4.3). After replacement, a full Precalibration is required followed by a complete Routine Autocalibration.

#### Memory Check failure

Whenever the **CAL** key is pressed, new calibration constants are checked to be within prescribed limits before being stored. Values outside prescribed limits flag a *Fail 6*. The same check is also performed:

- When the instrument is powered-up

- · Each time the output is switched ON

- During each self-test routine

#### CRITICAL PART CHANGES

Recalibration (or Verification) is necessary after replacement of a critical PCB assembly or a critical component. These are listed in Table 1.1 (see page 1-2), indicating the extent of the recalibration necessary.

#### Ohms Internal Adjustments

- If the Power Supply/Current Heatsink has been changed it may be necessary to adjust the quiescent bias current (IQ) by internal adjustment. Refer to Section 4.7 for further information.

- If a standard resistor value has been changed by subjecting it to undue stress, it may be possible to recalibrate by internal adjustment. Refer to Section 4.4 for further information.

#### Recalibration Procedures in Section 1

#### REMOTE CALIBRATION VIA THE IEEE 488 BUS

The device-dependent commands necessary for routine calibration of the instrument over the IEEE 488 bus are described in Section 5 of the User's Handbook. A guide-line example is given in Section 1.2 of this manual, but this needs to be adapted for the bus controller in use.

#### PRE-CALIBRATION PROCEDURES (Section 1.3)

In an initial internal calibration process at manufacture, certain 'Pre-cal' parameters are established in a special calibration memory.

Under certain conditions (detailed in *Table 1.1*) these parameters need to be re-established by completing the 'Pre-Cal' procedure before a Full Routine Autocalibration.

#### REMOTE PRE-CALIBRATION

A guide line example is given in Section 1.5, but this needs to be adapted for the bus controller in use.

| Assembly               | Components Replaced                                   | Calibration Required                   |

|------------------------|-------------------------------------------------------|----------------------------------------|

| Digital                | Complete Assembly                                     | Pre- & Routine Calibration             |

| (11.2)                 | Lithium Battery (Sect. 4.3)                           | Pre- & Routine Calibration             |

| •                      | Non-volatile RAM (M10/M23)                            | Pre- & Routine Calibration             |

|                        | Non-volatile RAM Supply                               |                                        |

|                        | commutation components                                | Pre- & Routine Calibration             |

| Reference Divider      | Complete Assembly                                     | Pre- & Routine Calibration             |

| (11.4)                 | Reference Assembly (11.4-1) Any set of main, guard or | Pre- & Routine Calibration             |

|                        | LSD switch FET's                                      | Pre- & Routine Calibration             |

|                        | Reference Buffer                                      | Pre- & Routine Calibration             |

|                        | Switch Driver Flip Flops or                           | The a riodinie dansiation              |

|                        | their preselected resistors                           | Pre- & Routine Calibration             |

|                        | R79                                                   | Pre- & Routine Calibration             |

|                        | 11/3                                                  | The a floatine campration              |

| DC Assembly            | Complete Assembly                                     | DC (All Ranges) only.                  |

| (11.5)                 | 1V attenuator R73/R74                                 | DC (1V, 100mV, 10mV, 1mV,              |

|                        | 100mV attenuator                                      | 100μV Ranges) only.                    |

|                        | R69/70/71/72/75/7672/75/76                            | DC (100μV - 100mV Ranges) only.        |

|                        | 100V/1000V attenuator                                 | DO (100μν - 100πν Hanges) only.        |

|                        | R8/9/25/26/46/47/64/65/88/95/98                       | DC (100V, 1000V Ranges) only.          |

|                        | 110/3/23/23/40/41/03/03/03/33/                        | Do (1000, 1000 v Haligoo, oliny.       |

| Sine Source            | Complete Assembly                                     | Specification Verification at          |

| (11.6)                 |                                                       | User's Discretion                      |

| AC Accombine           | Complete Accomply                                     | Routine Calibration                    |

| AC Assembly (11.7)     | Complete Assembly Sense Amplifier                     | Routine Calibration                    |

| (11.7)                 | Reference Inverter                                    | Routine Calibration                    |

|                        | AC/DC Transfer & Integrators                          | Routine Calibration                    |

|                        |                                                       | Hootine Calibration                    |

| Current/Ohms           | Complete Assembly                                     | DC/AC Current and Ohms                 |

| Current Assembly       | (N.B. Internal Adjustment required,                   | DC/AC Current                          |

| (11.8)                 | refer to Section 4.4)                                 |                                        |

|                        | +10 attenuator (R43/44)                               | DC Current                             |

|                        | (DCI function)                                        |                                        |

|                        | Current shunts R8/9/10/79/80                          | DC Current                             |

|                        | (DCI function)                                        | DO Guilleilt                           |

|                        | M8 and associated components                          | AC Current                             |

|                        | Current shunts                                        | AC Current                             |

|                        | Feedback resistor R45                                 | AC Current                             |

| Current/Ohms           | Standard Resistors, associated                        | Internal adjustment (Section 1.4)      |

| Ohms Assembly          | pre-selected/variable trimmer                         | Ohms calibration (replaced values only |

| (11.8)                 | resistors (Ohms function)                             | (.5)                                   |

| All Other Assemblies N | of Listed Above                                       | Specification Verification             |

|                        |                                                       | at User's Discretion                   |

Table 1.1

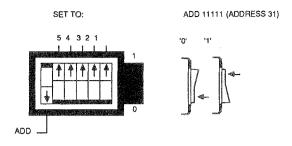

#### PREPARING THE 4808

Before any calibration is carried out, prepare the 4808 as follows:

- Turn on and allow a minimum of 2 hours to warm up in the specified environment.

- Cancel any MODE selection keys, ensure OUTPUT set to OFF.

- IEEE 488 Address switch:

Set to ADD 11111 (Address 31) unless the 4808 is to be calibrated via the IEEE 488 interface.

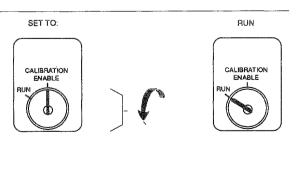

- 4. CALIBRATION ENABLE key switch: Insert Calibration Key and turn to ENABLE.

These actions activate the four calibration modes (labelled in red on the front panel), and present the cal legend on the MODE display.

#### Caution

Inadvertent use of the cal key can overwrite the calibration memory!

#### IEEE 488 ADDRESS

#### SECURITY KEYSWITCH

#### CAUTION:

Re-configuration of measurement circuitry should only be attempted when all voltage sources are OUTPUT OFF.

Before setting OUTPUT ON ensure the correct polarities have been selected and that any measurement device has been set to low sensitivity.

#### NOTE

The message Error 3 appears on the left-hand MODE display for any attempt to select an inappropriate mode.

#### WARNING:

Terminals marked with the symbol carry the output of the 4808. These terminals and any other connections to the load under test could carry lethal voltages. Under no circumstances should users touch any of the front (or rear) panel terminals unless they are first satisfied that no dangerous voltage is present.

#### **RETURNING THE 4808 TO USE**

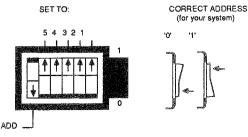

When any calibration is completed, return the 4808 to use as follows:

- 1. Ensure that Output off LED is lit.

- 2. CALIBRATION ENABLE key switch: Turn to RUN and withdraw calibration key.

- IEEE 488 Address switch: Restore to correct address if the 4808 is to be used in an IEEE 488 system.

The cal legend and calibration modes are deactivated.

#### **EQUIPMENT REQUIREMENTS**

Before removing the 4808 from service check that the necessary calibration equipment is available. The equipment summary, listed by function, relates to the procedures recommended in this handbook:

#### Caution

When choosing a set of current shunts ensure that their power dissipation ratings are sufficient to avoid permanent degradation from the self-heating effects of the current being checked. This applies particularly to the 1Amp shunt.

#### DC FUNCTION

Low Voltage (100mV to 10V)

An adjustable DC Voltage source of suitable accuracy

Example: Datron 4000A Autocal Standard

A battery-operated null detector with variable sensitivity, able to

withstand 1200V across its input terminals: Example: Keithley Instruments Model 155

High voltage (100V and 1000V)

A Precision Divider

Example: Datron 4902/S High Voltage Divider.

A battery-operated null detector with variable sensitivity, able to

withstand 1200V across its input terminals: Example: Keithley Instruments Model 155

Current (100µA to 1A)

A DC Voltmeter, of suitable accuracy standardized at 1V and

100mV.

Example: Datron 1281.

A set of calibrated current shunts of suitable accuracy.

Example: Tinsley 5685 "Wilkins" Standard Resistors.

#### **AC FUNCTION**

Voltage (1V to 1000V)

An Adjustable DC Voltage Source of suitable accuracy.

Example: Datron 4000 or 4000A Autocal Standard.

An AC/DC Thermal Transfer Standard capable of operating over

the range 1V to 1100V RMS. Example: Characterized Holt 6B 2-wire HF compensation (1V to 10V)

An AC DVM of suitable accuracy

Example: Datron 1281

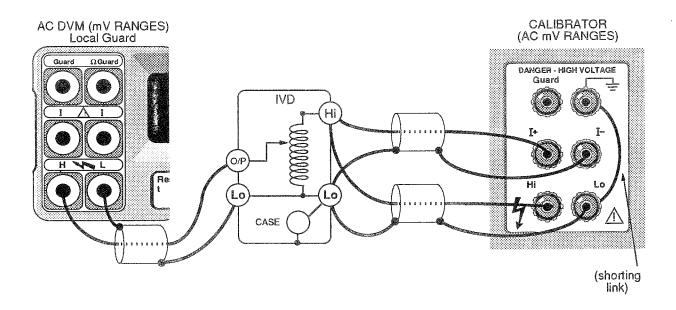

Millivolts at LF(1mV to 100mV)

A commercially-available Inductive Voltage Divider of suitable accuracy and frequency response; with ratios of 10:1, 100:1 and

1000:1.

Example: Tinsley 5560J

An AC DVM of suitable accuracy and frequency response.

Example: Datron 1281 or similar.

Millivolts at HF (1mV to 100mV)

An AC DVM of suitable accuracy and frequency response.

Example: Datron 1281 or similar.

Current (1mA to 1A)

A DC Current Source of suitable accuracy.

Example: Datron 4000 or 4000A Autocal Standard

AC/DC Thermal Transfer and a set of Calibrated Thermal-

Transfer Current Shunts of suitable accuracy. Example: Holt 6B and HCS-1 AC/DC Shunts.

An AC/DC transfer switching unit

Example: Holt HCS-1

Current (Alternate) (1µA to 1A)

A set of calibrated AC Shunts of suitable value and accuracy.

Example: Tinsley 5685 AC/DC Standard resistors.

An AC DVM of suitable accuracy and frequency response.

Example: Datron 1281 or similar.

A Buffer capable of operating with negligible errors from DC to

5kHz at a 1 Volt level

#### RESISTANCE

2-Wire & 4-Wire ( $10\Omega$  to  $100M\Omega$ )

A set of standard resistors covering  $10\Omega$  to  $100M\Omega$ . The  $10\Omega$  to  $10k\Omega$  should be 4-wire type.

Example:

For  $10\Omega - 10k\Omega$

Tinsley 5685

For  $100k\Omega - 10M\Omega$

Guildline 9330

An accurate resistance bridge, or other ratiometric device for measuring resistance to the required accuracy.

A Datron 1281 used as a transfer-measurement device.

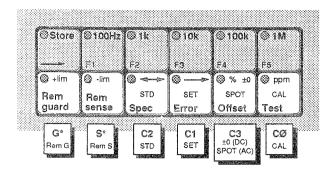

#### **AUTOCAL FACILITIES**

These keys are activated by two rear panel switches (refer to page 1-3 'Preparing the 4808'). When these modes are active, the legend 'cal' is presented on the left-hand MODE display.

The following is a general description of the facilities available. For specific information see the introduction proceeding each of the function's calibration routines.

#### CAL

The 4808 assumes that the selected range is to be calibrated at the exact Full Range value or at Zero. The instrument decides on 'Zero Offset' or 'Full Range Gain' from the right-hand OUTPUT display value (defined by the same limits as for 'SET'), and executes the calibration. If the value initially set on the OUTPUT display is below 2% of Full Range value, the instrument assumes that an offset calibration is requested, and if at 2% or above, a gain calibation is assumed.

#### CAL (with pre-selection)

If the CAL key is pressed after first pressing STD, SET or ±0, the CAL key executes, then cancels, the preselected AUTOCAL mode.

#### Caution

The following keys preselect an AUTOCAL mode, modifying the action of the CAL key.

#### SET

The SET key allows gain or offset calibration to a Calibration Standard value which cannot be adjusted to a nominal Full Range value or to absolute zero.

Before selecting SET, the  $\diamondsuit$  keys are operated to place the Calibration Standard value on the OUTPUT display and set the 4808 output level.

Pressing SET then informs the 4808 that calibration is to be carried out at this value. The instrument acknowledges by duplicating the value on the MODE display.

Next, the \$\infty\$ keys are manipulated to null the 4808 output against the Calibration Standard (the OUTPUT display changes during this adjustment).

Pressing the CAL key executes the calibration. The 4808 memorizes the difference between the two display values, and exits from SET mode. This is shown by transfer of the Standard value from the left-hand MODE display to the right-hand OUTPUT display. The instrument uses the difference to modify stored constants, which in 'RUN' mode correct both positive and negative outputs on the calibrated range only.

#### ±0 / SPOT

On the DCV function, the ±0 key is used to align the ON+ and ON- zeros of all DC voltage and current ranges, by a two part calibration on the 10V range. It is only necessary when the ON+ and ON- zeros of the 10V range do not coincide at the same null.

On the ACV and ACI function, the function of the key changes to SPOT Frequency calibration. When SPOT is pressed, the 4808 assumes that the spot frequency is to be changed, and so defaults the frequency to 1kHz. When used with SET, SPOT calibration can be carried out within 10% of the full range value, but when SPOT is used without SET, the 4808 assumes that the calibration is to be at Full Range. After SPOT calibration, selecting Spot Frequency at the calibrated value achieves the highest possible accuracy (see User's Manual, Section 4). It is only necessary to perform Spot Frequency calibration if the accuracy achievable is required in use. For recall procedures see the User's Manual page 4-10.

#### STD

#### Caution

Using the STD key changes the gain of all voltage and current ranges.

The STD key allows a user to re-standardize by trimming the value of the internal Master Reference voltage effectively changing the gain of all DC voltage and current ranges in the same ratio. The facility can be used to avoid a full recalibration of the 4808 when Laboratory References have been re-standardized (for instance when the instrument has been moved from one country to another).

First check  $\pm 0$  Alignment. The STD calibration is carried out on either the 1V or 10V range, using the DC Low Voltage procedure. Select STD after placing the Calibration standard value on the OUTPUT display. Continue the routine from step (1). Procedurally STD differs from SET only in the use of the STD key instead of the SET key.

#### GENERAL NOTES

#### INTERCONNECTIONS

It is recognised that interconnection instructions may need to be adapted to meet an individual user's requirements. It is assumed that users will possess some knowledge of the operation and use of standards equipment.

#### SENSE AVAILABILITY AS FOLLOWS

1V 10V 100V 1000V - Local/Remote Sense 1mV 10mV 100mV - Local Sense only All current ranges - not applicable (Local: 2-wire sense, Remote: 4-wire sense)

Output must be OFF to change sense connection (except that Remote changes automatically to Local when switching to Millivolt Ranges).

#### OUTPUT OFF DEFAULT WHEN UPRANGING

The 4808 cannot enter High-Voltage state with OUTPUT ON. Consequently, when ranging-up, the operating system allows the upranging to occur, but defaults to OUTPUT OFF for two specific cases:

- 1. When upranging to the 1000V Range.

- When upranging to the 100V Range:

To a voltage of 90V or more on DC

To a voltage of 75V or more on AC

Otherwise, OUTPUT remains ON when changing OUTPUT RANGE.

Refer to User's Handbook, Section 4.

#### GENERAL PROCEDURE

Prepare the instrument for calibration (refer to 'Preparing the 4808' procedure on page 1-3). Note that your instrument will not necessarily have all options fitted

The available options for the 4808 are as follows:

Option 10: DC Voltage function to ±200V.

Option 20: AC Voltage function to 200V.

Option 30: Integral 1000V amplifier for AC Voltage and/or DC Voltage functions. (Requires either Option

10, Option 20 or both.)

Option 40: Current converter to provide DC Current and AC Current functions. (DC Current capability requires Option 10, AC Current capability requires Option 20.)

Option 50: Resistance function. (Requires Option 10 or Option 20.)

Option 60: DC Current and/or AC Current range extension to 11A. This option includes the Datron 4600 Transconductance Amplifier and all necessary cabling. (Requires Option 40.)

The message 'Error 3' appears on the left-hand MODE display for any attempt to select an inappropriate mode. Select the equipment and procedures to be used. Set all sources to zero and all measurment devices to low sensitivity and configure using the interconnection diagram provided. If calibrating DC function, start with ±0 Alignment check routine. When all calibration has been completed use the 'Return to Use' routine on page 1-3.

#### **Calibration Routine**

Set the 4808 to OUTPUT ON and Full Range value. Adjust the 4808 output to equal the calibration standard and press CAL. The right-hand OUTPUT display changes to nominal.

#### Calibration Routine (with preselection)

The OUTPUT display is set to the Calibration Standard value, the 4808 output is switched ON, and one of the calibration mode preselector keys (STD, SET or  $\pm 0$ ) is pressed. The 4808 output is adjusted to equal the Calibration Standard value, and the CAL key is pressed to execute the calibration.

#### 1.2 REMOTE CALIBRATION GUIDELINES

The operation of the instrument in systems applications via the IEEE 488 interface, is described in Section 5 of the User's Handbook. In addition to its capability as a programmable calibrator, the 4808 can itself be calibrated under remote control. Full autocalibration of the instrument over the bus implies availability of a suitably programmed controller, programmable standards, programmable Null Detector, and a programmable Thermal Transfer.

Transfer of Calibration Facilities

#### Calibration Commands

The table below lists the device-dependant commands used for Routine Calibration. The relevant calibration codes are also listed.

These commands can only be activated when two conditions have been fulfilled:

- 1. the CALIBRATION ENABLE keyswitch on the instrument Rear Panel must be set to ENABLE, and

- the IEEE Interface command-code W1 must have been received and activated.

Additional commands can be activated when 'PRE-CAL ENABLE' switch is enabled. Refer to 1.5 Remote Pre-Calibration Guidlines.

When the 4808 is under remote control over the bus, the command-code WØ overrides the settings of the CALIBRATION ENABLE and internal PRE-CALIBRATION ENABLE switches, disabling the 'C' codes.

#### General Procedure

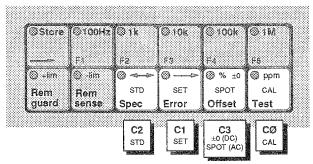

The Main Register is set to the Calibration Standard value (M\*\*\*...), the 4808 Output is switched ON (01), and one or a specified sequence of the calibration mode command codes (C1, C2, C3, I) may be transmitted.

The 'M' Code is adjusted to obtain a null at the Calibration Standard value, and  $C\emptyset$  is transmitted to execute the calibration.

#### Availability of Command Codes

| Command             | Description                                            | Functions and Facilities                                              |               |                   |               |                   |               |

|---------------------|--------------------------------------------------------|-----------------------------------------------------------------------|---------------|-------------------|---------------|-------------------|---------------|

| Codes<br>(Key caps) |                                                        | DC Voltage                                                            | DC Current    | AC Voltage        | AC Current    | 2-Wire Ω          | 4-Wire Ω      |

| CØ<br>(CAL)         | Range Zero                                             | 100mV-1000V<br>Ranges                                                 | All<br>Ranges |                   |               | 10Ω-1MΩ<br>Ranges |               |

|                     | Gain calibration<br>to Nominal Full Range              | 100mV-1000V<br>Ranges                                                 | All<br>Ranges | All<br>Ranges     | All<br>Ranges | 10Ω-1MΩ<br>Ranges | All<br>Ranges |

| *C1<br>(SET)        | Zero offset for range at User's selected value         | All<br>Ranges                                                         | All<br>Ranges |                   |               |                   |               |

|                     | Gain for range at<br>User's selected value             | All<br>Ranges                                                         | All<br>Ranges | All<br>Ranges     | All<br>Ranges |                   |               |

| *C2<br>(STD)        | Internal Reference<br>gain at user's<br>Standard value | 1V &10V<br>Ranges                                                     |               | 1V &10V<br>Ranges |               |                   |               |

| *C3<br>(±0)         | Alignment of internal ON+ and ON- zeros                | 10V<br>Range                                                          |               |                   |               |                   |               |

| Can                 | User's Message                                         | Refer to User's Handbook Section 5 'Programming of Bus Transmissions' |               |                   |               |                   |               |

<sup>\*</sup>Preselector - must be activated later by command code CØ (CAL)

#### COMMAND CODE FACILITIES (Routine Calibration)

For a General description see 'Autocal Facilities' page 1-5.

#### Calibration Codes

#### C1 (SET)

C1 gives calibration at any point in the selected range by allowing the user to input the value of the calibration standard used (initial M code used). Before executing the calibration CØ uses the final 'M' Code value to distinguish between Zero (offset calibration) and Full Range (gain calibration). The limits of Offset or Full Range depend on function selected (Refer to User's Handbook, Section 8).

#### C2 (STD)

C2 allows a user to compensate for changes of the internal Master Reference voltage. For best accuracy it is recommended this procedure is carried out in DC function. Note that the gains of all voltage and current ranges change in the same ratio. Execute with CØ.

#### CØ (execute pre-selection)

$C\emptyset$  executes one of the above preselected AUTO-CAL modes.

#### CØ (CAL only)

If Command CØ is sent without pre-selection code C1/C2 the instrument assumes that the selected range is to be calibrated at either Zero or Full Range. It uses the value input by the 'M' Code to distinguish between Zero (offset calibration) and Full Range (gain calibration) according to the function selected (Refer to User's Handbook, Section 8).

#### Guidelines - An Example

The following sequence suggests a method of calibrating the instrument 1V Range Gain against a buffered standard cell value of +1.018057V. It is assumed that the instrument is correctly addressed with its Calibration Keyswitch set to ENABLE and the instrument Output is OFF. Connect the Null Detector, set to low sensitivity, between the Standard Cell buffer and the 4808. The nulling operation is seperated into its own string, as it is likely to be iterative.

#### SET Calibration of 1V DC Gain FØR5GØSØW1M+1.018057C101=M(for null)CØ

The example suggests only the broad outline of one of many sequences which could be used to perform instrument calibrations.

#### Calibration Command Strings

The following AC command strings are given for the sole purpose of illustrating the methodology designed into the 4808 for remote calibration modes. Some reference to external operations is inferred. The nulling operation is seperated into its own string, as it is likely to be iterative.

It is assumed that the 4808 has previously been programmed in function and range (not autorange  $R\emptyset$ ) and that the external circuit is set up correctly. The 4808 is already programmed into its calibration mode by W1, with the calibration keyswitch set to ENABLE, and output OFF.

- a. Nominal Full Range LF Gain Calibration: H(LF)A101=M (for null)=CØ=OØ=

- b. Nominal Full Range HF Gain Calibration: H(HF)A1O1=M(for null)=CØ=OØ=

- c. Combined Nominal LF and HF Gain Cal: H(LF)A1O1=M(for null)=CO= H(HF)=M(for null)=CO=O0=

- d. Non-nominal LF Gain Calibration: H(LF) M(20%-200%FR)C1= O1=M(for null)=CØ=OØ=

- e. Non-nominal HF Gain Calibration: H(HF) M(20%-200%FR)C1= O1=M(for null)=CO=O0=

- f. Combined Non-nominal LF and HF Gain Cal:

H(LF)M(20%-200%FR)C1=

O1=M(for null)=CØ=

H(HF)M(20%-200%FR)C1=

M(for null)=CØ=OØ=

- g. Standardization at Nominal Full Range 1V or 10V Range only):

H(LF)A1C2O1=M(for null)=CØ=OØ=

- h. Standardization at a Non-nominal value (1V or 10V range only):

H(LF)M(20%-200%FR)C2=

O1=M(for null)=CØ=OØ=

#### 1.3 PRE-CALIBRATION

#### 1.3.1 Introduction

#### **GENERAL**

In an initial calibration process at manufacture, certain 'PRE-CAL' parameters are established in a special calibration memory to define the overall linearity of the instrument, and to allow maximum routine calibration memory span for adjustments. For normal purposes, these factory defined pre-calibration parameters are valid for the life of the instrument, and subsequent Routine Calibration procedures are sufficient to maintain calibration.

Preparation for the pre-calibration operation includes removal of the Top Cover, to facilitate selection of pre-calibration mode and operation of the calibration memory clear push-button. DC and AC pre-calibration must then be completed followed by a Full Routine Recalibration. Thereafter, all routine calibrations may be performed from the front panel or over the IEEE Interface without removing the covers.

#### Circumstances Calling for Pre-Calibration

The stored parameters are invalidated by replacement of certain critical parts of the instrument.

- The Lithium battery which powers the whole calibration memory when the instrument supply is switched off. This should be replaced at five-year intervals (Refer to Section 4.3).

- The Digital Assembly

- · The Reference Divider Assembly

- Critical components in the Digital or Reference Divider, AC and Sine Source assemblies

A full list appears on flap of page 1-2. After replacement of any of these parts, new parameters must be stored in the pre-calibration memory, by procedures (in manual or remote control) detailed in this section.

#### **EQUIPMENT REQUIREMENTS**

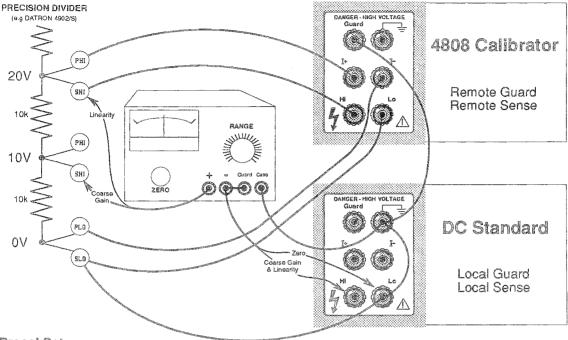

#### DC

- A precision divider capable of dividing 20.000,000V to 10.000,000V to a ratio error of better than 0.1ppm between tappings. For example a Datron 4902/S precision divider or alternatively a Datron 4903 DC Calibration Unit.

- A DC 10V reference with an accuracy of better than 2ppm.

Example: Datron Instruments 4000A or a bank of standard cells.

#### AC

- A precision voltmeter capable of 1V AC measurement with a stability between readings of better than ±5ppm.

Example: Datron Instruments 1281

- An inductive voltage divider with ratios of x1.0 and x0.1 capable of dividing 10.000,00V to 1.000,000V to an accuracy better than 2ppm.

- An AC/DC Thermal Transfer Standard.

Example: Holt Model 6B

#### PREPARING THE 4808

Before clearing the pre-calibration store, prepare the 4808 as described on page 1-3. The adjustments detailed in the following sequences include intentionally clearing the instrument's pre-calibration memory, which loses ALL previous calibration information. Therefore before proceeding make certain that the reasons for carrying out a complete recalibration are valid. (If in any doubt, consult your Datron Service Centre)

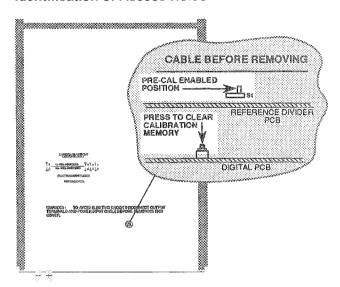

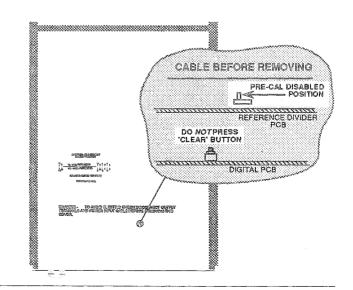

#### Identification of Access Holes

These holes provide access to the 'PRE-CAL ENABLE' switch and the 'CLEAR CALIBRATION MEMORY' switch.

- a. Release 6 screws retaining the top cover.

- b. Lift the top cover at the front of the instrument and locate the two holes which give access to the two-position 'PRE-CAL ENABLE' switch and the press-button 'CLEAR CALIBRATION MEMORY' switch.

- c. Locate the hole which gives access to the PRE-CALENABLE switch. Insert an insulated tool in the hole and move the precal switch to the right (Enable). The legend 'cal', as presented on the left-hand MODE display, also appears on the righthand OUTPUT display.

#### Caution

The following operation (d.) clears all the calibration memory stores as part of pre-calibration. Proceed only if this is required.

- d. Locate the hole which gives access to the Calibration Memory CLEAR push-button. Insert an insulated tool in the hole and press the button to clear the calibration memory.

- c. Refit the top cover but do not secure.

Complete the following pre-calibration procedure (Paras 1.3.2 overleaf).

#### 1.3.2 Procedure

#### DCV Precal

#### ± Zero Calibration

First complete the ±0 Alignment Calibration Procedure in Section 8 of the User's Handbook, but with pre-calibration mode selected.

DCV Precal Setup

Ensure the 4808 Output off LED is lit, cancel any MODE keys, select Remote Sense and deselect Remote Guard. Select DCV FUNCTION and 10V RANGE. Connect the Precision Divider to the instrument terminals as shown. Use short leads.

#### Coarse Gain

#### a. 4808

Ensure OUTPUT OFF and select the 10V RANGE.

#### b. Precision Divider/Null Detector

Set the Null Dectector to Low sensitivity and connect to the Precision Divider at 10V tapping.

#### c. 4808

Connect to the precision divider as shown. Select ON+ with zero OUTPUT.

#### d. DC Standard/Null Detector

If the DC Standard is a buffered bank of standard cells, switch the Buffer output to zero. However if an electronic reference is used connect Null Detector -ve lead to Reference Low.

Set Null Detector to high sensitivity. Zero Null Detector. Reduce Null Detector sensitivity.

Switch on or reconnect the  $10V\ DC$  Standard Hi to Null detector.

#### e. 4808

Select SET, its LED lights. Adjust the OUTPUT keys for Full Scale OUTPUT (+19.999999V).

Use instrument OUTPUT  $\diamondsuit$  keys to adjust the Null Detector reading to zero.

Press CAL: the SET LED goes out.

#### Linearity

#### f. Precision Divider/Null Detector

Reduce Null Detector sensitivity. Reconfigure Null Detector Hi to divider 20V tapping.

#### g. DC Standard/Null Detector

If the DC Standard is a buffered bank of standard cells, switch the Buffer output to zero. However if an electronic reference is used, connect the Null Detector -ve lead to the DC Standard's Low terminal.

Set Null Detector to high sensitivity. Zero Null Detector. Increase Null Detector sensitivity.

Switch on or reconnect the 10V reference Hi to Null detector.

#### h. 4808

Select STD, its LED lights. Press ON+ and Full Range OUTPUT (10.000000V).

#### j. Null Detector

Increase Null Detector sensitivity and use 4808 OUTPUT \$\infty\$ keys to adjust the reading to zero.

#### k 4808

Press the CAL key: the STD LED goes OFF. Pre-cal is now completed. Select OUTPUT OFF and disconnect.

#### ACV LF Precal

#### **ACV LF Precal Linearity Setup**

Ensure the 4808 Output off LED is lit, cancel any MODE keys, select Remote Sense and deselect Remote Guard. Select ACV FUNCTION and connect the IVD to the instrument terminals as shown. Use short leads. Select the 1kHz Frequency Range.

#### 10% Range

- a. IVD Select x1.0 ratio.

- b. 4808

Select 10V range, at 1kHz on the 1kHz Frequency range. Select 1.000,00V. Press the ±0 key, its LED lights. Use instrument OUTPUT \$\infty\$ keys to adjust the DVM reading to 1V. Press CAL: the ±0 LED remains lit and 1.000,00V (nominal 10% Full Range) appears on the right-hand OUTPUT display.

#### Full Range

- c. IVD Select the x0.1 ratio to divide the 4808 output by 10.

- d. 4808

Select Full Range. Use instrument OUTPUT  $\diamondsuit$  keys to adjust the DVM reading to 1V. Press the CAL key: the  $\pm 0$  LED goes OFF. Recheck, without pre-selection, at 1V and 10V. If required repeat the procedure. Select OUTPUT OFF and disconnect. Pre-cal is now completed. Disable pre-cal and complete a Full Routine Calibration.

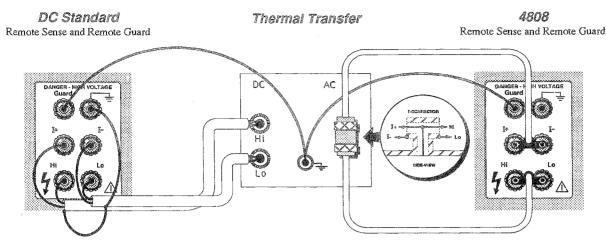

#### **ACV HF Precal**

#### ACV HF Precal Linearity Setup

With OUTPUT OFF, connect the 4808 and DC Voltage Standard to the Thermal Transfer AC and DC inputs, respectively.

#### 10% Range

#### a. 4808

On AC function, select the 10V range, select the 1MHz frequency rangeand use the FREQUENCY  $\diamondsuit$  keys to display 1MHz. Use the OUTPUT  $\diamondsuit$  keys to output 1V and set OUTPUT ON. Press the SPOT key.

- b. DC Voltage Standard

Set to 1V output and set OUTPUT ON.

- c. Thermal Transfer Standard Configure for DCV measurement at the 1V level and adjust for Null. Configure for ACV measurement at the 1V level.

- d. 4808

Use the OUTPUT  $\diamondsuit$  keys to adjust the OUTPUT display reading to obtain a null on the Thermal Transfer Standard. Press the CAL key.

#### Full Range

- e. DC Voltage Standard Set to 10V Output, select OUTPUT ON.

- f. Thermal Transfer Standard Configure for DCV measurement at the 10V level and adjust for Null. Configure for ACV measurement at the 10V level.

- g. 4808

Press Full range key to display 10V and use the OUTPUT \$\infty\$ keys to obtain a null on the Thermal Transfer. Press the CAL key.

#### PRE-CAL DISABLE

When pre-calibration is complete the pre-cal enable switch must be set to RUN.

CAUTION: DO NOT press the internal push-button which clears the calibration memory. If this is done, any parameters stored in the calibration memory are cleared; so precalibration is cancelled, and must be repeated.

- a. Lift the top cover at the front.

- Locate the hole which gives access to the PRE-CALENABLE switch.

- c. Insert an insulated tool in the hole Pre-cal and move the switch to the left (RUN). The legend 'cal' remains on the MODE display, but disappears from the OUTPUT display.

- d. Refit and secure the top cover.

A Full Routine Calibration is necessary before completion of the Return to Use procedure on page 1-3.

#### 1.4 INTERNAL OHMS ADJUSTMENT

#### Introduction

The Autocal procedure for routine calibration of the 4808's Resistance function is described in Section 8 of the User's Handbook.

The method of calibration is to measure the value of each standard resistor, and store the measured value in non-volatile calibration memory. Subsequently, each time are sistance RANGE is selected, the previously calibrated value is displayed.

If a standard resistor has been subjected to undue stress, its value may have moved outside its tolerance (signalled by an *Error 6* message during Routine Autocalibration). If the value is less than approx. 50ppm outside tolerance, it can be adjusted internally using a variable trimmer. For values out of tolerance in excess of 50ppm it is likely that the resistor has been over-stressed, in which case consult your Datron Service Centre.

#### **Manual Trimming Procedure**

The following procedure is a supplement to Routine Autocalibration. It is necessary only when the 4-wire calibration detailed in Section 8 of the User's Handbook has resulted in an 'Error 6' message.

It can also be used when, for operational reasons, it is necessary to adjust a resistor to its nominal value. For this purpose a continuously-reading method of measurement is convenient.

- a. Release eight screws retaining the top cover.

- b. Lift the top cover at the front of the instrument and locate the 8 holes giving access for 'Ω OPTION ADJUSTMENT'.

- c. Insert an insulated screw driver tool in the hole for the range selected, and adjust the preset resistor (rotating clockwise increases the resistance value).

- d. Re-measure the 4-wire value and repeat operation (c) until the desired value is obtained.

- e. Re-calibrate the range for 4-wire and 2-wire connections as detailed in Section 8 of the User's Handbook.

- Repeat the manual trimming procedure above for all ranges as required.

- g. Finally refit and secure the top cover using the eight screws removed in (a), above.

#### 1.5 REMOTE PRE-CALIBRATION GUIDELINES

Transfer of DC pre-calibration facilities

Transfer of AC pre-calibration facilities

#### General Procedure

The transfer of Pre-calibration facilities to remote control is illustrated above. The general procedure follows that for remote Routine Calibration; the external circuit is connected as for manual pre-calibration.

These commands can only be activated when the following conditions have been fulfilled:

- The CALIBRATION ENABLE keyswitch on the instrument. Rear Panel must be set to ENABLE.

- Ensure that the IEEE address switch is set correctly.

- The IEEE Interface command-code W1 must have been received and activated.

- The internal PRE-CAL ENABLE switch is set to ENABLE.

When the 4808 is under remote control over the bus, the command code WØ overrides the setting of the CALIBRATION ENABLE and internal PRE-CAL ENABLE switches, disabling the 'C' codes.

#### Pre-Calibration Command Strings

The following command strings are given for the sole purpose of illustrating the methodology for the remote pre-calibration mode. Some reference to external operations is inferred. The nulling operation is separated into its own string, as it is likely to be iterative.

It is assumed that the external circuit is set up correctly.

The 4808 has already been programmed into its calibration mode by W1, with the CALIBRATION ENABLE keyswitch and the internal PRE-CAL ENABLE switch set to ENABLE.

The calibration memory stores have been cleared, and the 4808 Output is OFF.

The string sequence for DC pre-calibration is as follows:

#### 1. ±Zero

| FØR6M+ØO1C3= | (Set-up and ±0 preselection)  |

|--------------|-------------------------------|

| $M^{***}=$   | (Iterative nulling operation) |

| CØ=M-Ø=      | ('CAL' and -ON)               |

| M***=        | (Iterative nulling operation) |

| CØ=OØ=       | ('CAL' then OUTPUT OFF)       |

#### 2. Coarse Gain and Linearity

| FØR6C4M+19.99999901= | (Set-up and linearity         |

|----------------------|-------------------------------|

|                      | preselection)                 |

| M***=                | (Iterative nulling operation) |

| CØ=0Ø=               | ('CAL' then OUTPUT OFF)       |

| C5=M+10.00000001=    | (Set-up and linearity         |

|                      | preselection)                 |

| M***=                | (Iterative nulling operation) |

| CØ=0Ø=               | ('CAL' then OUTPUT OFF)       |

The string sequence for AC pre-calibration is as follows:

Full Range and 1/10th Range Linearity; first for LF, and then for HF

| F1R6H***C3O1=M***= | (Program to frequency and     |

|--------------------|-------------------------------|

|                    | voltage)                      |

| $M^{***}=$         | (Iterative nulling operation) |

| CØ=M***=           | (First 'CAL' of two-part      |

|                    | process)                      |

| M***=              | (Iterative nulling operation) |

| CØ=0Ø              | (Second 'CAL' cancels         |

preselected mode)

#### Notes on the Use of the Null Detector

The Null Detector is normally connected in series with the 4808 Hi lead. A high-impedance-input device should be chosen to reduce off-null currents due to differences in the outputs of the DC voltage source and the 4808. A battery-operated instrument is preferred to ensure adequate isolation.

Some Null Detectors possess high input impedance only when their readings are on-scale, so care should be taken to ensure that drain currents from the DC Voltage source do not become excessive. This applies particularly if the DC source is a standard cell or a bank of cells.

#### Six points are important:

- The null detector should be connected to the 4808 (or 4808 loadresistor) only when the 4808 Output off LED is lit. (with output OFF, the I+, I-, Hi and Lo terminals are at high impedance).

- Always set the null detector to its lowest sensitivity before connecting up, and increase sensitivity only when the voltages output by the DC Voltage source and the 4808 are close in value.

- Do not change polarity of the 4808 or DC Voltage source without first switching the 4808 OUTPUT OFF. Care must be taken to ensure that the correct polarity on key is pressed, to avoid excessive voltages being connected across the null detector, particularly when checking the 4808 directly against a standard cell.

- 4. Most Null Detectors are equipped with a 'Self-zero' or 'Zero-check' facility. For maximum accuracy, the Null Detector range zero should be checked before each calibration nulling operation is performed. However, when gain-calibrating the 4808 Voltage and Current Ranges, the zero offset of the calibration voltage source is nullified by adjustment of the Null Detector zero control. This setting should not be altered until the corresponding Range gain has been calibrated.

#### 5. WARNING

During performance checks and calibration a common mode voltage equal to the full range voltage is present at the Null Detector input terminals. On 1000V checks this voltage is potentially lethal, so EXTREME CAUTION must be observed when making adjustments to the null detector sensitivity.

#### 6. CAUTION

The Null Detector used must be able to withstand voltages up to 1200V between its input terminals. Such voltages will be present during the time that the 4808 is ramping from zero to 1000V Full range after setting OUTPUT ON. Inadvertent disconnection of the Precision Divider terminals can transfer full output across the Null detector.

| • |  |  |   |  |

|---|--|--|---|--|

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

| 9 |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

| ! |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  | • |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

#### **Calibration Source Zero Offsets**

It is common practice to accept a small offset in the output of a voltage calibration standard, providing that the same offset is present at all output values, including zero.

A more difficult situation arises if there is a 'DC turnover offset' between the source's positive and negative output values. In this case, a difference in DC value will be observed when switching the source between its positive and negative outputs with zero volts selected. This type of error is normally adjusted out on the 4808 by a preliminary '±0' calibration on the 10V Range, to a null detected across its output terminals. This sets both ON+ and ONzeros to the same DC level; and as the same linear analog circuitry is used to generate both output polarities, range calibration of zero and gain in positive polarity is then all that is required.

The 4808 analog circuitry is fully floating, so its output may be referred to any common mode voltage within the range specified in Section 6.3 of the User's Handbook. In particular, each Range zero may be aligned to absolute zero in Local Sense by calibration to a null across its Hi and Lo (Sense) terminals. But if it is then gain-calibrated against an offset source without re-zeroing to that source's offset zero, normal mode gain errors will result. It is therefore essential that any offset in the source's output be nullified before gain calibration is carried out. This can be done at Range zero, simply by trimming the Null Detector null.

The notional sequence of calibration for the 4808 should be as follows:

#### a. ±0

Check that the 10V Range 'ON+' and 'ON-' zeros coincide at absolute zero (Adjust if necessary).

#### b. Range Zeros

Carry out 'ON+' zero calibration on all Ranges against the same absolute zero.

#### c. Range Gain

Each Range Gain in turn, (Null Detector connections as shown for Voltage or Current)

- At 'ON+' zero output from both source and 4808, trim the Null Detector for null.

- ii. At the required positive DC level, calibrate the 4808 Range gain.

This sequence ensures that the 4808 'ON+' and 'ON-' zeros are both set to absolute zero, and that both positive and negative polarities are accurately gain-calibrated to a unipolar source.

If it is required to check the 4808 'ON-' gain calibrations against a bipolar source, the source's 'ON-' zero offset must first be nullified, as described in (c. i.) opposite.

|   | , |  |  |  |

|---|---|--|--|--|

| - |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

#### SECTION 2 FAULT DIAGNOSIS

#### WARNING

HAZARDOUS ELECTRICAL POTENTIALS ARE EXPOSED WHEN THE INSTRUMENT COVERS ARE REMOVED.

ELECTRIC SHOCK CAN KILL

#### CAUTION